Getting Started with Vivado

For the most up to date version of this guide, please visit Getting Started with Vivado for Hardware-Only Designs.

Prerequisites

Prior to starting this guide make sure to install Vivado. For more information see our Installing Vivado guide.

Introduction

The goal of this guide is to familiarize the reader with the Vivado tools through the hello world of hardware, blinking an LED.

This guide was created using Vivado 2016.2.

1. Starting Vivado

Windows

Open the start menu and go to All Programs→Xilinx Design Tools→Vivado <version>→Vivado <version>

2. The Start Page

This is the screen that displays after Vivado starts up. The buttons are described below using the image as a guide.

1. Create New Project

This button will open the New Project wizard. This wizard steps the user through creating a new project. The wizard is stepped through in section 3.

2. Open Project

This button will open a file browser. Navigate to the desired XPR file and click Open to open the project in Vivado.

3. Open Example Project

This will guide the user through creating a new project based on an example project. These projects will not work on all devices.

4. Open Hardware Manager

This will open the Hardware Manager without an associated project. If connecting to and programming a device is all that is required by the user this is the button to use.

3. Creating a New Project

3.2

The text in the dialog describes the steps that will be taken to create a project. Click Next to continue to the first step.

3.3

The first step is to set the name of the project. Vivado will use this name when generating its folder structure.

Important: Do NOT use spaces in your project name or location path. This will cause problems with Vivado. Instead use an underscore, a dash, or CamelCase.

3.4

Now that the project has a name and a place to save important files we need to create the necessary source files. To add a Verilog or VHDL file click the create file button.

3.5

This will open the Create Source File dialog, shown below. This dialog has three options for the new file. The first is the type of file. This allows for selecting between different HDL file types, Verilog, VHDL, Verilog Header, and SystemVerilog. The final type available is the Memory File option. This is used for memory device initialization, most of the time this can be ignored.

The second box is for the file name. Enter the name for the file to create. Including the file extension is optional, Vivado will add one based on the file type selected. The final option is where to store the file. Most of the time this can be left as <Local to Project>.

Important: Do NOT use spaces in your file name. This will cause problems with Vivado. Instead use an underscore, a dash, or CamelCase.

3.6

It is also possible to import source files into the project. In the Add Sources dialog click the Add Files button and navigate to the source file to import into the project. Unless there is reason not to, make sure that the Copy sources into project check box is checked to make a copy of the source file local to the project. Since the file is copied, any changes made to the file inside one project do not affect the original file.

3.7

After adding the HDL files and clicking Next in the main dialog, the next dialog is displayed. This dialog is for adding IP to the project. This is used in more advanced designs and is outside the scope of this guide. Click Next.

3.8

The next section is for adding a constraints file. Constraints files control how signals are routed, define clocks, and define timing constraints. Click the Create File button to open the Create Constraints File dialog.

3.9

Again the dialog presents three options. the file name and file location have the same properties as the ones in the Create Source File dialog. What is different is the file types that can be created. The only option available is XDC which stands for Xilinx Design Constraints. This file will define clocking, pin mapping, and timing restrictions.

Important: Do NOT use spaces in your file name. This will cause problems with Vivado. Instead use an underscore, a dash, or CamelCase.

3.10

Now that the necessary files have been created it is time to choose the target device. There are two ways to choose a target. The first is from the actual on board component and the second is from installing the appropriate board files and picking a board.

3.10.1

To pick a target from the on board component find the part number for the IC and find it in the selection list. There are two places to find a part number for our boards. The first is to look at the actual component on the board and try to discern the writing. The other is to look on the reference page for the target board.

3.10.2

To pick a target from the boards list, install the board files prior to creating a new project. Then select the board to use as a target from the list.

3.11

The next section gives a summary of the options selected throughout the wizard. Verify that the information looks correct and click Finish.

3.12

Since new source files were created, Vivado will now show a new dialog box for defining a module for each new source file that it was told to create. Here the inputs and outputs of a module can be defined.

Each section can be interpreted as follows:

| Field | Description | Example |

|---|---|---|

| Port Name | The name to give the new port | leds |

| Direction | Is the port an input, output, or bi-directional | output |

| Bus | Is the port a bus/multiple bits? | x |

| MSB | What is the Most Significant Bit? | 7 |

| LSB | What is the Least Significant Bit? | 0 |

Fill out the port definitions for clk and led as shown then click OK.

4. The Flow Navigator

The Flow Navigator is the most important pane to know. It is how a user navigates between different Vivado tools.

The Navigator is broken into seven sections:

- Project Manager

- Allows for quick access to project settings, adding sources, language templates, and the IP catalog

- IP Integrator

- Tools for creating Block Designs

- Simulator

- Allows a developer to verify the output prior to programming their device

- RTL Analysis

- lets the developer see how the tools are interpreting their code

- Synthesis

- Gives access to Synthesis settings and post-synthesis reports

- Implementation

- Gives access to Implementation settings and post-implementation reports

- Program and Debug

- Access to settings for bitstream generation and the Hardware Manager

5. The Project Manager

This tool is where most development will occur and is the initial tool open after creating a new project.

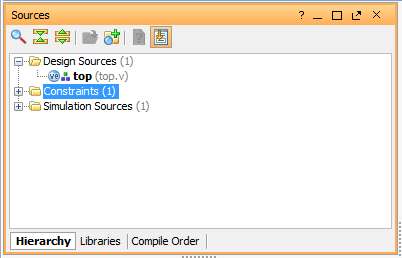

The Sources pane contains the project hierarchy and is used for opening up files. The folder structure is organized such that the HDL files are kept under the Design Sources folder, constraints are kept under the Constraints folder, and simulation files are kept under the Simulation Sources folder. Files can be opened in the Workspace by double-clicking on the corresponding entry in the Sources pane. Sources can also be added by either right clicking the folder to add the file to and selecting Add Sources or by clicking the Add Sources button ( ).

).

The Properties pane allows for viewing and editing of file properties. When a file is selected in the Sources pane its properties are shown in here. This pane can usually be ignored.

The Results pane consists of several different useful tools for debugging a project. The most important one to know is the Messages tool. This tool parses the Tcl console for errors, warnings, and other important information and displays it in an informative way.

The Tcl console is a tool that allows for running commands directly without the use of the main user interface. Some messages may direct to the Tcl console for more information regarding an error.

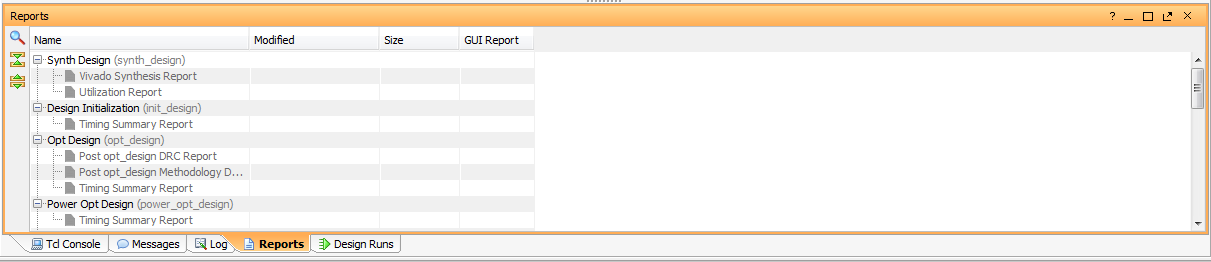

The Reports tool is useful for quickly jumping to any one of the many reports that Vivado generates on a design. These reports include power, timing, and utilization just to name a few.

The Log displays the output from the latest Synthesis, Implementation, and Simulation runs. Digging into this is not necessary as the reports and messages view store the information in the log in a more readable format.

The last tool is the Design Runs. Using this tool run settings can be edited and new runs can be created. This tool is useful when targeting multiple devices with the same design.

6. Writing HDL and Constraints

To actually get the board to blink an LED, code needs to be written in both the Verilog and the constraints files. Opening up the Verilog file (top.v in this guide) this window should open in the workspace area.

Between lines 26 and 27 add the following code:

reg [24:0] count = 0; assign led = count[24]; always @ (posedge(clk)) count <= count + 1;

If the Genesys 2, NetFPGA-1G-CML, or NetFPGA-SUME is being targeted, clear the contents of the whole file and replace it with the following:

module top( input clk_p, input clk_n, output led ); wire clk; IBUFGDS #( ) clk_inst ( .O(clk), .I(clk_p), .IB(clk_n) ); reg [25:0] count = 0; assign led = count[25]; always @ (posedge(clk)) count <= count + 1; endmodule

This is different because those boards have a input clock that uses differential logic. If you want to know more read this article on low-voltage differential signalling.

Now open the XDC file. At the moment it is empty so paste in the code below depending on the target board.

| Constraint File Source Code | |

|---|---|

| Board | Constraint Code |

| Arty | set_property -dict { PACKAGE_PIN E3 IOSTANDARD LVCMOS33 } [get_ports clk]

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports clk]

set_property -dict { PACKAGE_PIN H5 IOSTANDARD LVCMOS33 } [get_ports led]

|

| Basys 3 | set_property -dict { PACKAGE_PIN W5 IOSTANDARD LVCMOS33 } [get_ports clk]

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports clk]

set_property -dict { PACKAGE_PIN U16 IOSTANDARD LVCMOS33 } [get_ports led]

|

| CmodA7 | set_property -dict { PACKAGE_PIN L17 IOSTANDARD LVCMOS33 } [get_ports clk]

create_clock -add -name sys_clk_pin -period 83.33 -waveform {0 41.66} [get_ports clk]

set_property -dict { PACKAGE_PIN A17 IOSTANDARD LVCMOS33 } [get_ports led]

|

| Genesys 2 | set_property -dict {PACKAGE_PIN AD11 IOSTANDARD LVDS} [get_ports clk_n]

set_property -dict {PACKAGE_PIN AD12 IOSTANDARD LVDS} [get_ports clk_p]

create_clock -period 5.000 -name sys_clk_pin -waveform {0.000 2.500} -add [get_ports clk_p]

set_property -dict {PACKAGE_PIN T28 IOSTANDARD LVCMOS33} [get_ports led]

|

| Nexys 4 | set_property -dict { PACKAGE_PIN E3 IOSTANDARD LVCMOS33 } [get_ports clk]

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports clk]

set_property -dict { PACKAGE_PIN T8 IOSTANDARD LVCMOS33 } [get_ports led]

|

| Nexys 4 DDR | set_property -dict { PACKAGE_PIN E3 IOSTANDARD LVCMOS33 } [get_ports clk]

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports clk]

set_property -dict { PACKAGE_PIN H17 IOSTANDARD LVCMOS33 } [get_ports led]

|

| Nexys Video | set_property -dict { PACKAGE_PIN R4 IOSTANDARD LVCMOS33 } [get_ports clk]

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports clk]

set_property -dict { PACKAGE_PIN T14 IOSTANDARD LVCMOS25 } [get_ports led]

|

| NetFPGA-1G-CML | set_property -dict { PACKAGE_PIN AA2 IOSTANDARD LVDS } [get_ports clk_n]

set_property -dict { PACKAGE_PIN AA3 IOSTANDARD LVDS } [get_ports clk_p]

create_clock -add -name sys_clk_pin -period 5.00 -waveform {0 2.5} [get_ports clk_n]

set_property -dict { PACKAGE_PIN E17 IOSTANDARD LVCMOS33 } [get_ports led]

|

| NetFPGA-SUME | set_property -dict { PACKAGE_PIN G18 IOSTANDARD LVDS } [get_ports clk_n]

set_property -dict { PACKAGE_PIN H19 IOSTANDARD LVDS } [get_ports clk_p]

create_clock -add -name sys_clk_pin -period 5.00 -waveform {0 2.5} [get_ports clk_n]

set_property -dict { PACKAGE_PIN AR22 IOSTANDARD LVCMOS15 } [get_ports led]

|

| ZedBoard | set_property -dict { PACKAGE_PIN Y9 IOSTANDARD LVCMOS33 } [get_ports clk]

create_clock -add -name sys_clk_pin -period 10.00 -waveform {0 5} [get_ports clk]

set_property -dict { PACKAGE_PIN T22 IOSTANDARD LVCMOS33 } [get_ports led]

|

| Zybo | set_property -dict { PACKAGE_PIN L16 IOSTANDARD LVCMOS33 } [get_ports clk]

create_clock -add -name sys_clk_pin -period 8.00 -waveform {0 4} [get_ports clk]

set_property -dict { PACKAGE_PIN M14 IOSTANDARD LVCMOS33 } [get_ports led]

|

Once that is done the code is ready to be “compiled.”

8. Synthesis, Implementation, and Bitstream Generation

In order to create a file that can be used to program the target the “compilation-pipeline” needs to be done.

This starts with Synthesis. Synthesis turns HDL files into a transistor level description based on timing and I/O constraints. To run Synthesis click either  in the toolbar or

in the toolbar or  in the Flow Navigator. The output of Synthesis is then passed to Implementation.

in the Flow Navigator. The output of Synthesis is then passed to Implementation.

Implementation has several steps. The steps that are always run are Opt Design (Optimize the design to fit on the target FPGA), Place Design (Layout the design in the target FPGA fabric), and Route Design (Route signals through the fabric). To run Implementation click either  in the toolbar or

in the toolbar or  in the Flow Navigator. This output is then passed on to the Bitstream Generator.

in the Flow Navigator. This output is then passed on to the Bitstream Generator.

The Bitstream Generator generates the final outputs needed for programming the FPGA. To run Bitstream Generation click either  in the toolbar or

in the toolbar or  in the Flow Navigator. With no settings changed, the generator will create a BIT file.

in the Flow Navigator. With no settings changed, the generator will create a BIT file.

9. The Hardware Manager

The Hardware Manager is used for programming the target device.

The first step to programming a device is to connect to it. There are two ways to do this.

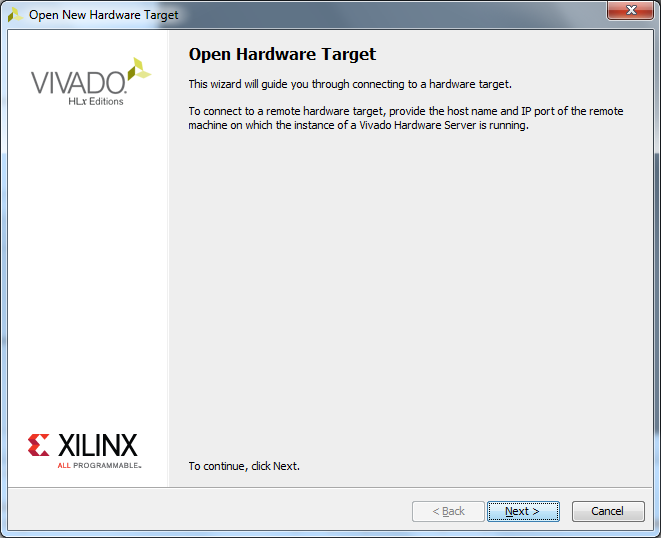

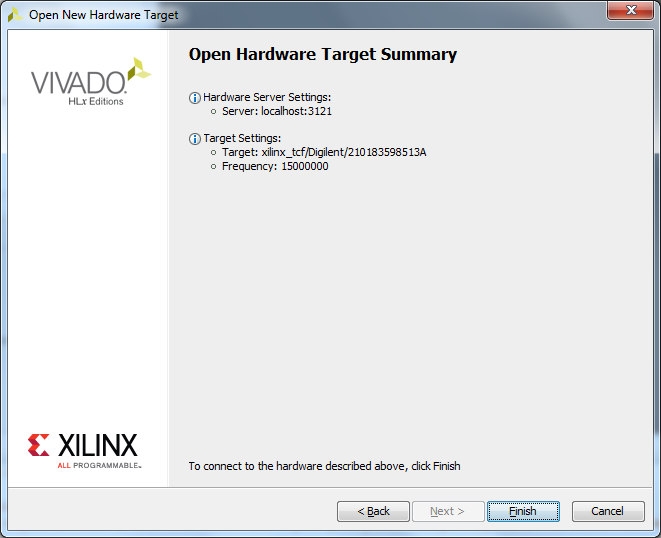

1. Open New Hardware Target

The first method is to manually open the target. This is required if the hardware is connected to another computer. To get to the Open Hardware Target wizard either open the Hardware Manager and click the  link in the green banner or click the

link in the green banner or click the  button in the Flow Navigator under

button in the Flow Navigator under  . From the dropdown that opens select

. From the dropdown that opens select  . The wizard will open, click Next.

. The wizard will open, click Next.

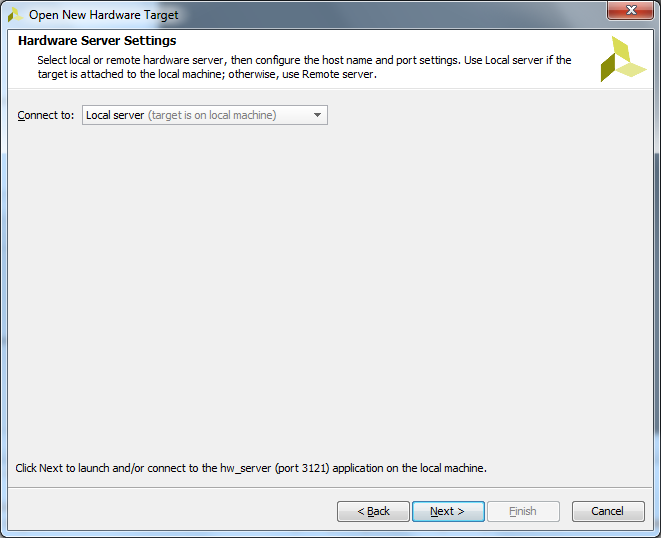

The next screen asks if the hardware server is local or remote. If the board is connected to the host computer choose local, if it is connected to another machine choose remote and fill in the Host Name and Port fields appropriately. Click Next.

This screen gives a list of devices connected to the hardware server. If there is only one connected it should be the only device shown. If there are multiple connected determine the serial number of the device to connect to and find it in the list. Click Next.

The final screen shows a summary of the options selected in the wizard. Verify the information and click Finish. The board is now connected to the hardware manager.

2. Auto-Connect

The second method is to automatically open the target. To get to the  button either open the Hardware Manager and click the

button either open the Hardware Manager and click the  link in the green banner or click the

link in the green banner or click the  button in the Flow Navigator under

button in the Flow Navigator under  . From the dropdown that opens select

. From the dropdown that opens select  . Vivado will attempt to find a hardware server running on the local machine and will connect to the device on the server.

. Vivado will attempt to find a hardware server running on the local machine and will connect to the device on the server.

Programming

To program the device with the BIT file generated earlier either click the  link in the green banner or click the

link in the green banner or click the  button in the Flow Navigator under

button in the Flow Navigator under  . From the dropdown that opens select the device to program (Example:

. From the dropdown that opens select the device to program (Example:  ) and the following window will open:

) and the following window will open:

The Bitstream File field should be filled in with the bit file generated earlier. If not, click the  button at the right end of the field and navigate to

button at the right end of the field and navigate to

<Project Directory>/<Project Name>.runs/impl_1/ and select the bit file (Example:  ). Now click Program. This will connect to the board, clear the current configuration, and program using the new bit file.

). Now click Program. This will connect to the board, clear the current configuration, and program using the new bit file.