Programmable Logic

Digilent FPGA and SoC boards provide easy access to Xilinx FPGAs, with a variety of peripherals to suit your application needs, and the built-in programming circuits to ease the bring-up and testing of your design. Whether you are just dipping your toe into FPGA design for the first time, or you are developing complex designs with cutting-edge hardware, the boards below can help.

This page details the variety of features of our boards. If you want to dive deeper into the reference materials for any particular board, check out its Resource Center, linked below.

| Product Name | FPGA/SoC Part | Expansion Connectors | Multimedia Interfaces | Connectivity | User I/O | Programming Interfaces | Memory |

|---|---|---|---|---|---|---|---|

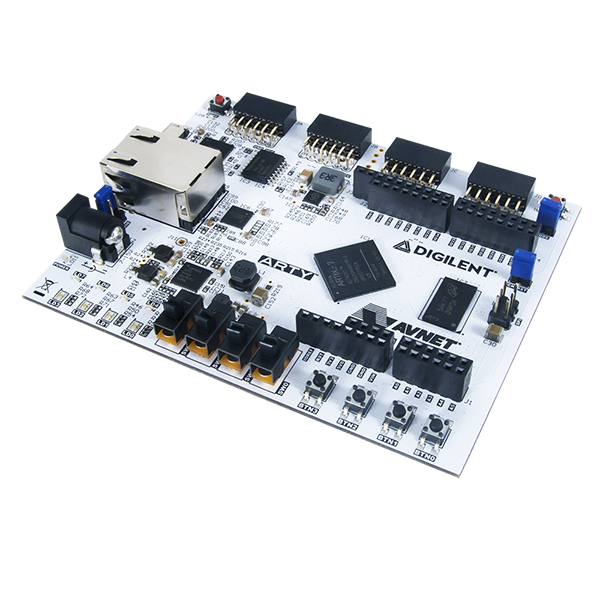

Arty A7  | Artix-7 (XC7A100T/XC7A35T) | • 4x Pmod • Arduino Shield Connector | N/A | • USB-UART • 10/100 Ethernet | • 4 Buttons • 4 Switches • 4 LEDs • 4 RGB LEDs | • USB-JTAG • QSPI Flash | • 256 MB DDR3L • 16 MB QSPI Flash • 4,860 Kb BRAM (A7-100T) / 1,800 Kb BRAM (A7-35T) |

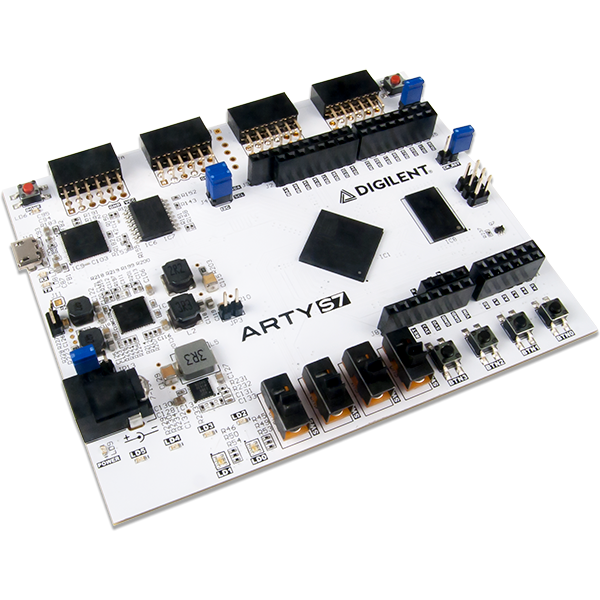

Arty S7  | Spartan-7 (XC7S50/XC7S25) | • 4x Pmod • Arduino Shield Connector | N/A | • USB-UART | • 4 Buttons • 4 Switches • 4 LEDs • 2 RGB LEDs | • USB-JTAG • QSPI Flash | • 256 MB DDR3L • 16 MB QSPI Flash • 2,700 Kb BRAM (S7-50) / 1,620 Kb (S7-25) |

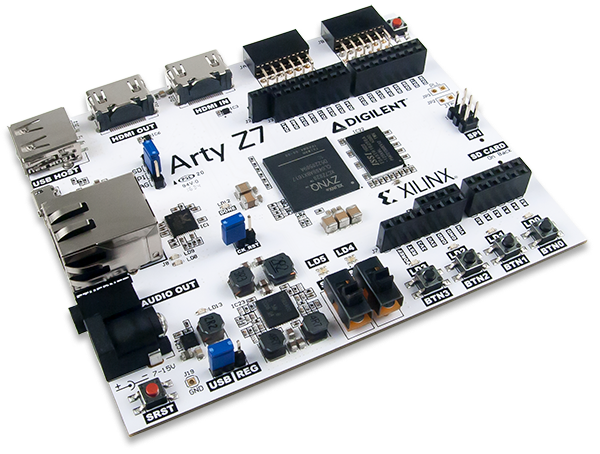

Arty Z7  | Zynq-7000 (XC7Z020/XC7Z010) | • 2x Pmod • Arduino Shield Connector | • HDMI Sink • HDMI Source • PWM Mono Audio Output Jack | • USB-UART • Gigabit Ethernet • USB 2.0 Host PHY | • 4 Buttons • 2 Switches • 4 LEDs • 2 RGB LEDs | • USB-JTAG • QSPI Flash • microSD | • 512 MB DDR • 16 MB QSPI Flash • 4.9 Mb BRAM (Z7-20) / 2.1 Mb BRAM (Z7-10) • microSD card slot |

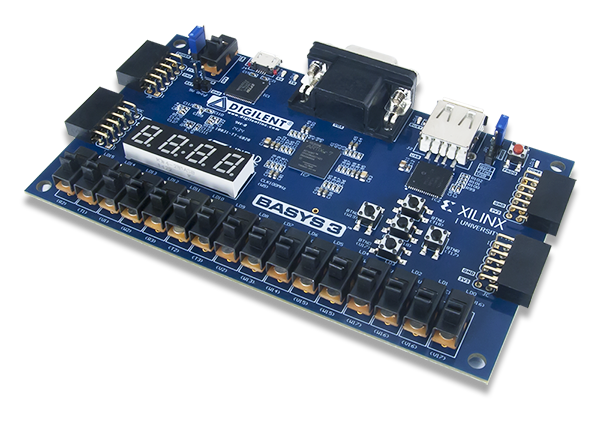

Basys 3  | Artix-7 (XC7A35T) | • 3x Pmod | • VGA Output | • USB-UART • USB HID Host Port | • Seven-Segment Display • 5 Buttons • 16 Switches • 16 LEDs | • USB-JTAG • QSPI Flash • USB Drive | • 1,800 Kb BRAM • 4 MB QSPI Flash |

Cmod A7  | Artix-7 (XC7A35T/XC7A15T) | • 48-pin DIP Connector • 1x Pmod | N/A | • USB-UART | • 2 Buttons • 2 LEDs • 1 RGB LED • 2 Analog Inputs | • USB-JTAG • QSPI Flash | • 512 KB SRAM • 1,800 Kb BRAM (A7-35T) / 900 Kb BRAM (A7-15T) • 4 MB QSPI Flash |

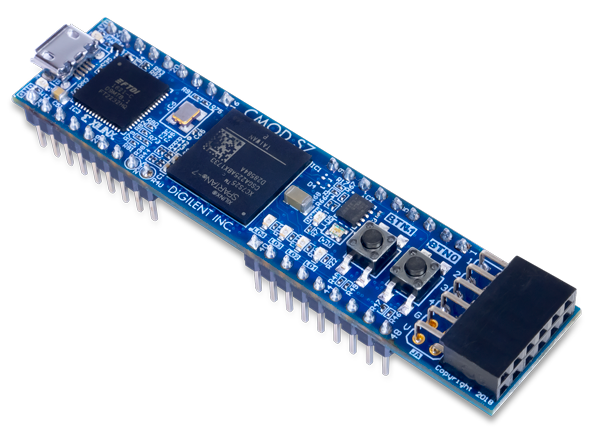

Cmod S7  | Spartan-7 (XC7S25) | • 48-pin DIP Connector • 1x Pmod | N/A | • USB-UART | • 2 Buttons • 4 LEDs • 1 RGB LED • 2 Analog Inputs | • USB-JTAG • QSPI Flash | • 1,620 Kb BRAM • 4 MB QSPI Flash |

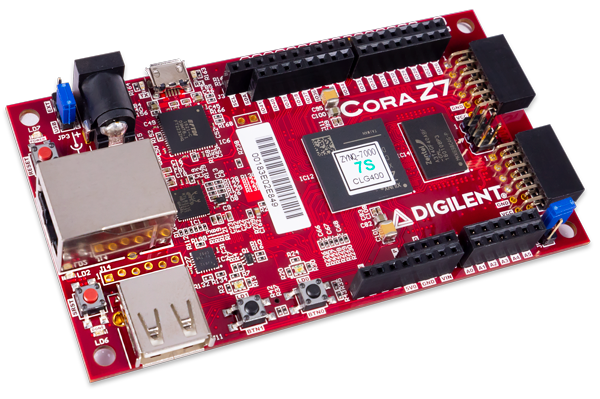

Cora Z7  | Zynq-7000 (XC7Z010/XC7Z007S) | • 2x Pmod • Arduino Shield Connector | N/A | • USB-UART • Gigabit Ethernet • USB 2.0 Host PHY | • 2 Buttons • 2 RGB LEDs | • USB-JTAG • microSD card slot | • 512 MB DDR3 • 2.1 Mb BRAM (Z7-10) / 1.8 Mb BRAM (Z7-07S) • microSD card slot |

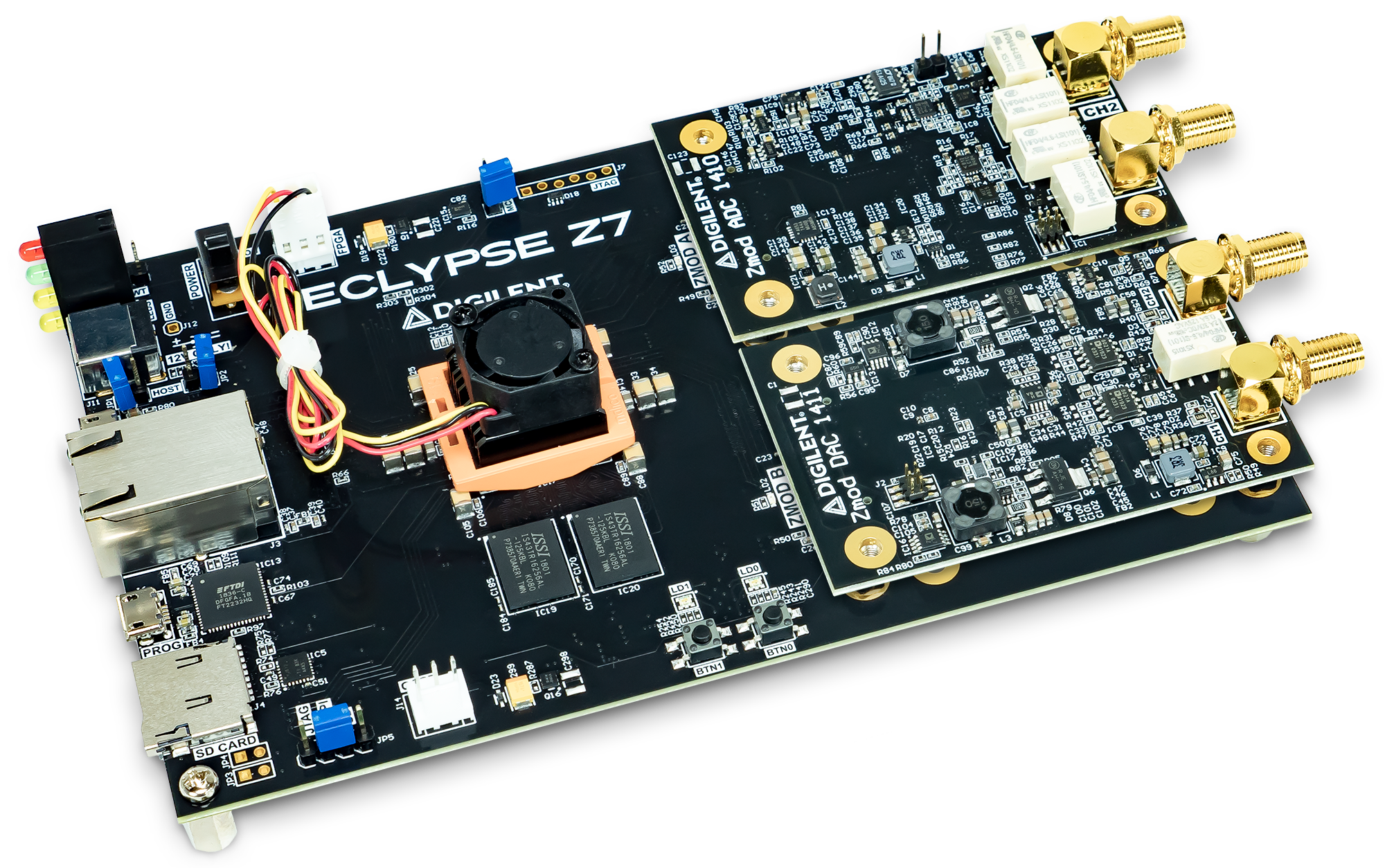

Eclypse Z7  | Zynq-7000 (XC7Z020) | • 2x Zmod • 2x Pmod | N/A | • USB-UART • Gigabit Ethernet • USB 2.0 Host/Device/OTG PHY | • 2 Buttons • 2 RGB LEDs | • USB-JTAG • QSPI Flash • microSD | • 1 GB DDR3L • 16 MB QSPI Flash • 4.9 Mb BRAM • microSD card slot |

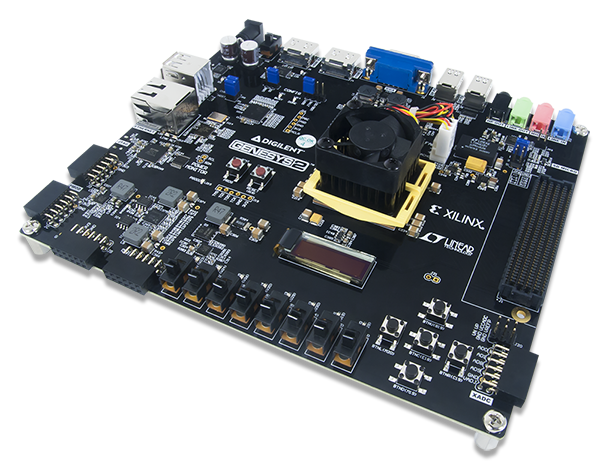

Genesys 2  | Kintex-7 (XC7K325T) | • 1x FMC HPC • 5x Pmod (1 Digital/Analog) | • HDMI Sink • HDMI Source • VGA Output • Audio Codec with 4 Audio Jacks | • USB-UART • Gigabit Ethernet • USB MSD/HID Host Port • USB 2.0 Host/Device/OTG PHY | • 6 Buttons • 8 Switches | • USB-JTAG • QSPI Flash • microSD • USB Drive | • 1 GB DDR3 • 32 MB QSPI Flash • 16,020 Kb BRAM • microSD card slot |

Genesys ZU  | Zynq UltraScale+ (XCZU5EV/XCZU3EG) | • 1x Zmod • 4x Pmod (1 Digital/Analog) • 1x FMC LPC • 1x FMC Gigabit (ZU-5EV only) • dual-slot Mini PCIe/mSATA | • 2x Pcam Camera Connectors • DisplayPort Source • HDMI Source and Sink (ZU-5EV only) • Audio Codec with 4 Audio Jacks | • USB-UART • USB-C • 2.4 GHz Wi-Fi • Gigabit Ethernet • SFP+ 10G Ethernet (ZU-5EV only) • USB 2.0 Host PHY with 2x USB Type-A ports | • 5 LEDs • 1 RGB LED • 7 Buttons • 4 Switches | • USB-JTAG • QSPI Flash • microSD • USB | • 4 GB DDR4 • 32 MB QSPI Flash • 7.6 Mb BRAM (ZU-3EG) / 5.1 Mb BRAM (ZU-5EV) • 18.0 Mb UltraRAM (ZU-5EV Only) • microSD card slot |

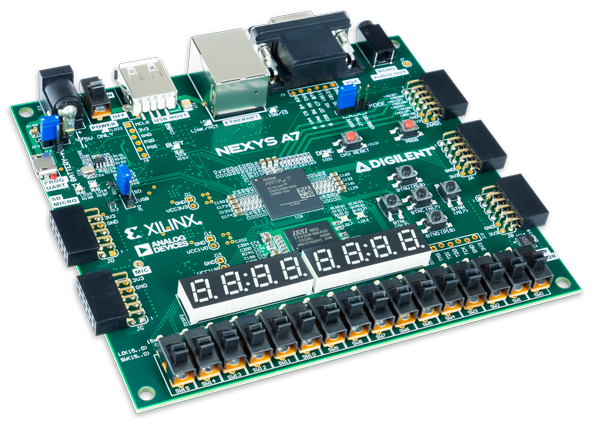

Nexys A7  | Artix-7 (XC7A100T/XC7A50T) | • 5x Pmod (1 Digital/Analog) | • VGA Output • PWM Audio Output • PDM Microphone | • USB-UART • 10/100 Ethernet • USB HID Host Port | • Seven-Segment Display • 5 Buttons • 16 Switches • 16 LEDs • 2 RGB LEDs • Temperature Sensor | • USB-JTAG • QSPI Flash • microSD • USB Drive | • 128 MB DDR2 • 16 MB QSPI Flash • 4,860 Kb BRAM (A7-100T) / 2,700 Kb BRAM (A7-50T) • microSD card slot |

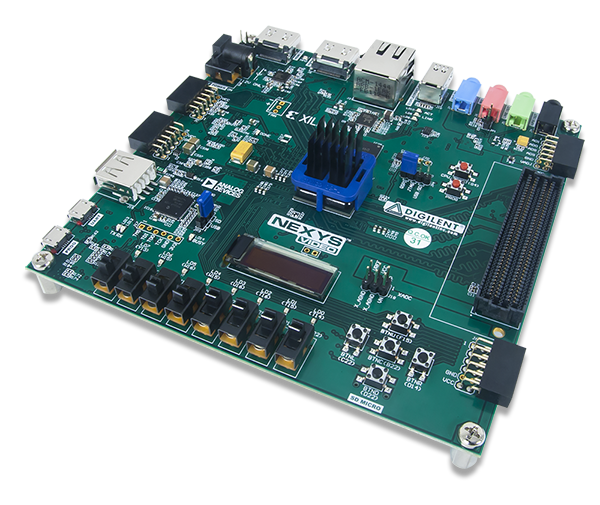

Nexys Video  | Artix-7 (XC7A200T) | • 4x Pmod (1 Digital/Analog) • 1x FMC LPC | • HDMI Sink • HDMI Source • DisplayPort Source • Audio Codec with 4 Audio Jacks | • USB-UART • Gigabit Ethernet • USB HID/MSD Host Port | • OLED Display • 5 Buttons • 8 Switches • 8 LEDs | • USB-JTAG • QSPI Flash • microSD • USB Drive | • 512 MB DDR3 • 32 MB QSPI Flash • 13,140 Kb BRAM • microSD card slot |

USB104 A7  | Artix-7 (XC7A100T) | • 1x Zmod • 3x Pmod | N/A | • USB-UART • USB Data Transfer Interfaces | • 2 Buttons • 4 LEDs | • USB-JTAG • QSPI Flash | • 512 MB DDR3 • 16 MB QSPI Flash • 4,860 Kb BRAM |

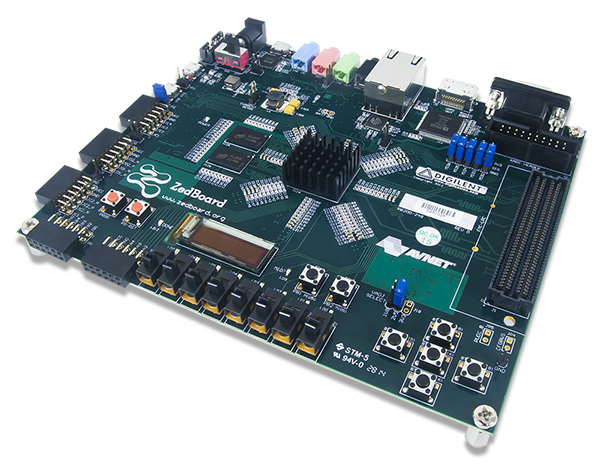

ZedBoard  | Zynq-7000 (XC7Z020) | • 5x Pmod (1 connected to MIO) • 1x FMC LPC | • HDMI Source • VGA Output | • USB-UART • Gigabit Ethernet • USB 2.0 OTG | • OLED Display • 7 Buttons • 8 Switches • 9 LEDs • Analog Mixed Signal Header | • USB-JTAG • QSPI Flash • microSD | • 512 MB DDR3 • 32 MB QSPI Flash • 4.9 Mb BRAM • microSD card slot |

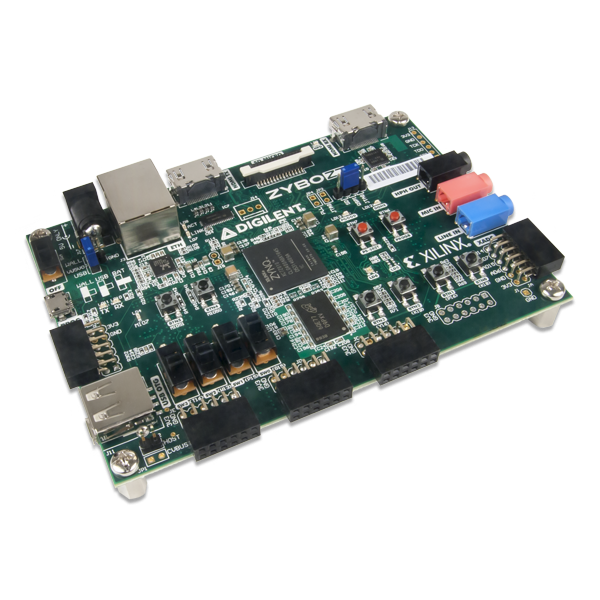

Zybo Z7  | Zynq-7000 (XC7Z020/XC7Z010) | • 6x* Pmod Ports (1 Digital/Analog and 1 connected to MIO on both variants, *5x on Z7-10) | • HDMI Sink • HDMI Source • Pcam Camera Connector • Audio Codec with 3 Audio Jacks | • USB-UART • Gigabit Ethernet • USB 2.0 Host/Device/OTG PHY | • 6 Buttons • 4 Switches • 5 LEDs • 2 RGB LEDs | • USB-JTAG • QSPI Flash • microSD | • 1 GB DDR3L • 16 MB QSPI Flash • 4.9 Mb BRAM (Z7-20) / 2.1 Mb BRAM (Z7-10) • microSD card slot |

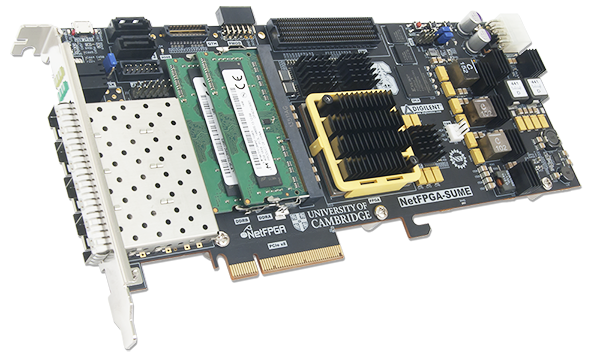

NetFPGA-SUME  | Virtex-7 (XC7VX690T) | • 1x QTH Connector • x8 PCIe Gen. 3 Edge Connector • 1x FMC HPC • 1x I2C Pmod | N/A | • USB-UART • Four 10G SFP+ Interfaces | • 2 Buttons • 2 LEDs | • USB-JTAG • Flash | • 2x 4 GB DDR3 SODIMMs • 3x 72 Mb QDRII+ SRAMs • 2x SATA III Ports • Flash for FPGA bitstreams • microSD card slot |

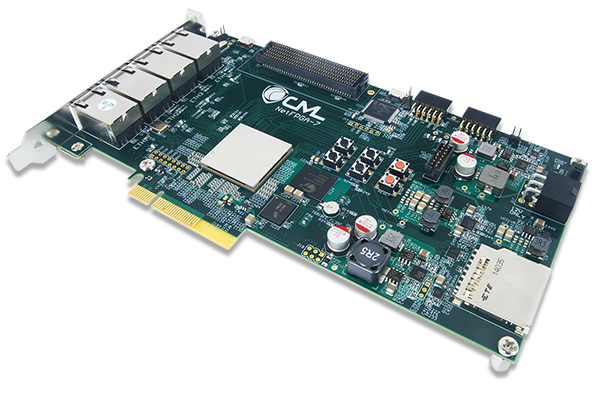

NetFPGA-1G-CML  | Kintex-7 (XC7K325T) | • 2x Pmod • 1x FMC HPC | N/A | • USB-UART • Four Gigabit Ethernet PHYs • Gen. 2 PCIe | • 4 Buttons • 4 LEDs | • USB-JTAG • BPI Flash • USB Drive | • 512 MB dynamic RAM • 4.5 MB static RAM • 1 Gb BPI Flash • 16,020 Kb BRAM • SD card slot |

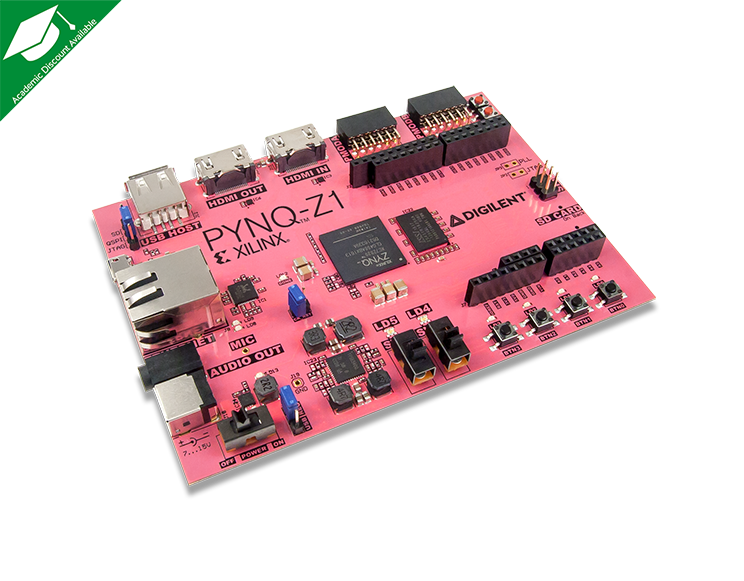

PYNQ-Z1  | ZYNQ-7000 (XC7Z020-1CLG400C) | • 2x Pmod • Arduino Shield Connector | • HDMI sink • HDMI source • PWM Mono Audio Output Jack • Electret microphone with PDM output | • Gigabit Ethernet PHY • USB OTG PHY (supports host only) • USB-UART bridge | • 4 Buttons • 2 Switches • 4 LEDs • 2 RGB LEDs | • USB-JTAG • QSPI Flash • microSD | • 512MB DDR3 • 16MB Quad-SPI Flash • MicroSD slot |

All Boards

- For Internal Use Only : All Pages in this Namespace

-