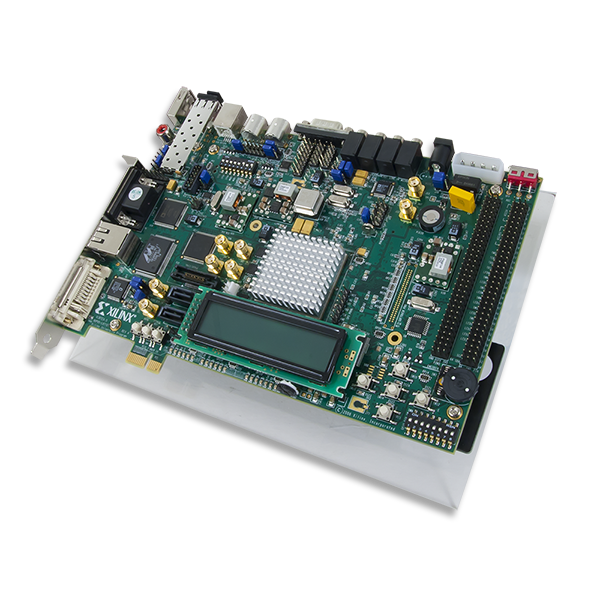

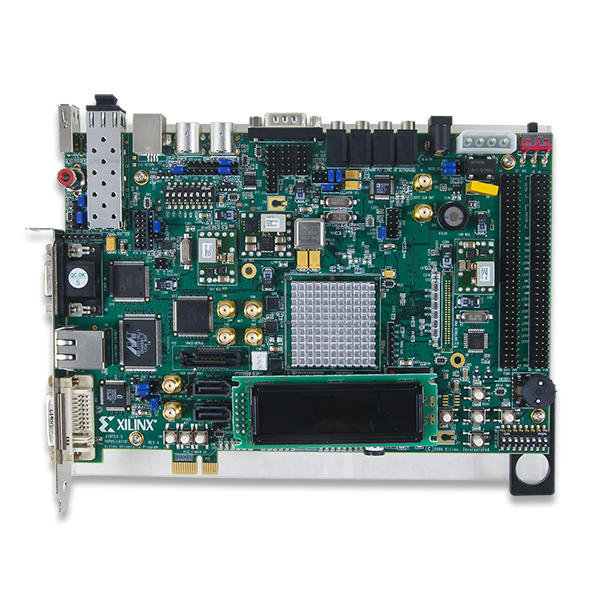

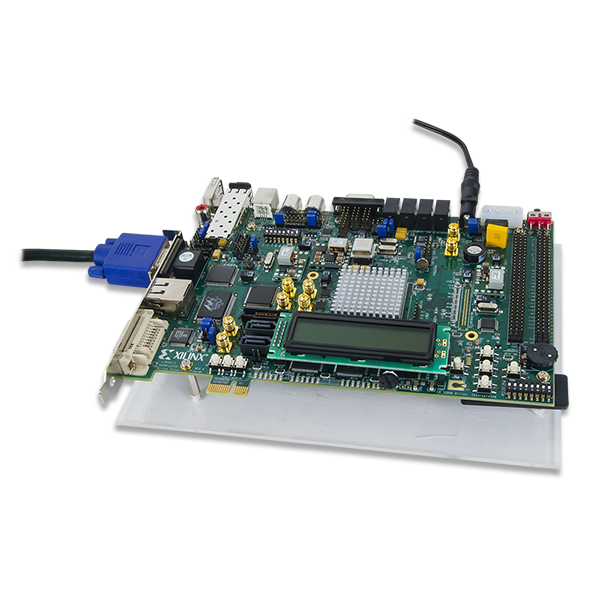

Virtex-5 OpenSPARC

- JTAG programming interface

(32Mbyte each)

supporting MII, GMII, RGMII,

and SGMII interfaces

line out, headphone, microphone,

and SPDIF digital audio jacks

Note

The Virtex-5 OpenSPARC is retired and no longer for sale in our store.

The Virtex®-5 OpenSPARC Evaluation Platform is a powerful system for hosting the OpenSPARC T1 open-source microprocessor. Equivalent to the Xilinx® ML509 board and based on the Xilinx XUPV5-LX110T FPGA, this kit brings the throughput of OpenSPARC Chip Multi-Threading to an FPGA.

OpenSPARC T1 is the open-sourced version of the custom designed UltraSPARC T1 microprocesor from Sun Microsystems. To broaden the appeal of this state-of-the-art Chip Multi-threading (CMT) technology to the developers, engineers at Sun Microsystems and Xilinx Inc. have developed a reference design that allows a scaled-down version of the OpenSPARC T1 processor to run on Xilinx Virtex-5 FPGAs. This reference design is an excellent starting point for researchers and entrepreneurs to build and test novel ideas in the areas of computer architecture, logic design, parallel programming, and compiler techniques, among others. For more details on how to download the OpenSPARC design and the reference design, please visit www.opensparc.net/fpga.