Using a Digilent FPGA Github Demo's Releases (2020.1)

Warning

This page is for internal use only. It is intended to be embedded within other wiki pages and does not provide the full context necessary to use these steps

Hardware Only Release (Before Programming)

Note: This workflow is common across many Digilent FPGA demos. Screenshots may not match the demo you are working with.

Important: These steps are only to be used with releases for Xilinx tools versions 2020.1 and newer. Older releases may require other flows, as noted in the table of releases.

First, download and extract the '*.xpr.zip' file from the demo release, linked above.

- Open a Vivado Project from a Release

-

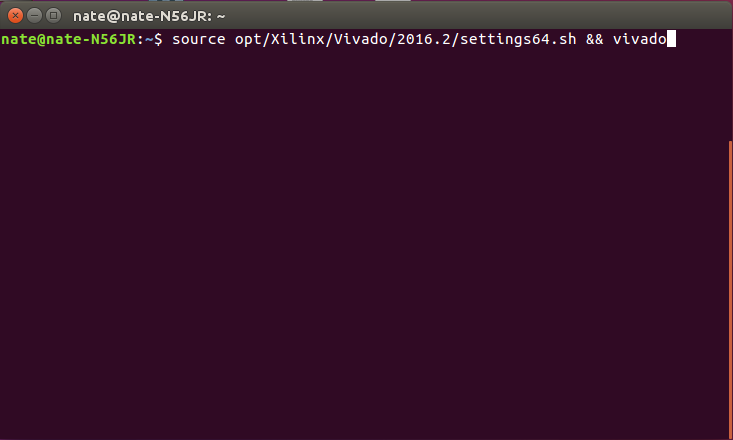

Launch Vivado

Select the dropdown corresponding to your operating system, below.

- Windows

- Linux

- Build a Vivado Project

-

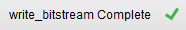

Note that if your project already has a generated bitstream, as indicated by the status in the top right corner of the window reading “write_bitstream Complete!”, then you can skip this section.

Generate a Bitstream

In order to create a file that can be used to program the target board, each stage of the “compilation pipeline” needs to be run.

This starts with Synthesis. Synthesis creates a description of the logic gates and connections between them required to perform the functionality described by the HDL files, given the constraints included in XDC files. To run Synthesis click either

in the toolbar or

in the toolbar or  in the Flow Navigator. The output of Synthesis is then passed to Implementation.

in the Flow Navigator. The output of Synthesis is then passed to Implementation.

Implementation has several steps. The steps that are always run are Opt Design (Optimize the design to fit on the target FPGA), Place Design (Lay out the design in the target FPGA fabric), and Route Design (Route signals through the fabric). To run Implementation click either

in the toolbar or

in the toolbar or  in the Flow Navigator. This output is then passed on to the Bitstream Generator.

in the Flow Navigator. This output is then passed on to the Bitstream Generator.

The Bitstream Generator generates the final output file needed for programming the FPGA. To run Bitstream Generation click either

in the toolbar or

in the toolbar or  in the Flow Navigator. With no settings changed, the generator will create a '.bit' file.

in the Flow Navigator. With no settings changed, the generator will create a '.bit' file.

Depending on the complexity of the design, the board used, and the strength of your computer, the process of building the project can take between 5 and 60 minutes. When complete, a pop-up dialog will appear, prompting you to select one of several options. None are relevant for the purposes of this guide, so click Cancel. The “write_bitstream complete” status message can be seen in the top right corner of the window, indicating that the demo is ready to be deployed to your board.

Hardware Only Release (Programming)

- Program a Bitstream onto an FPGA Board

-

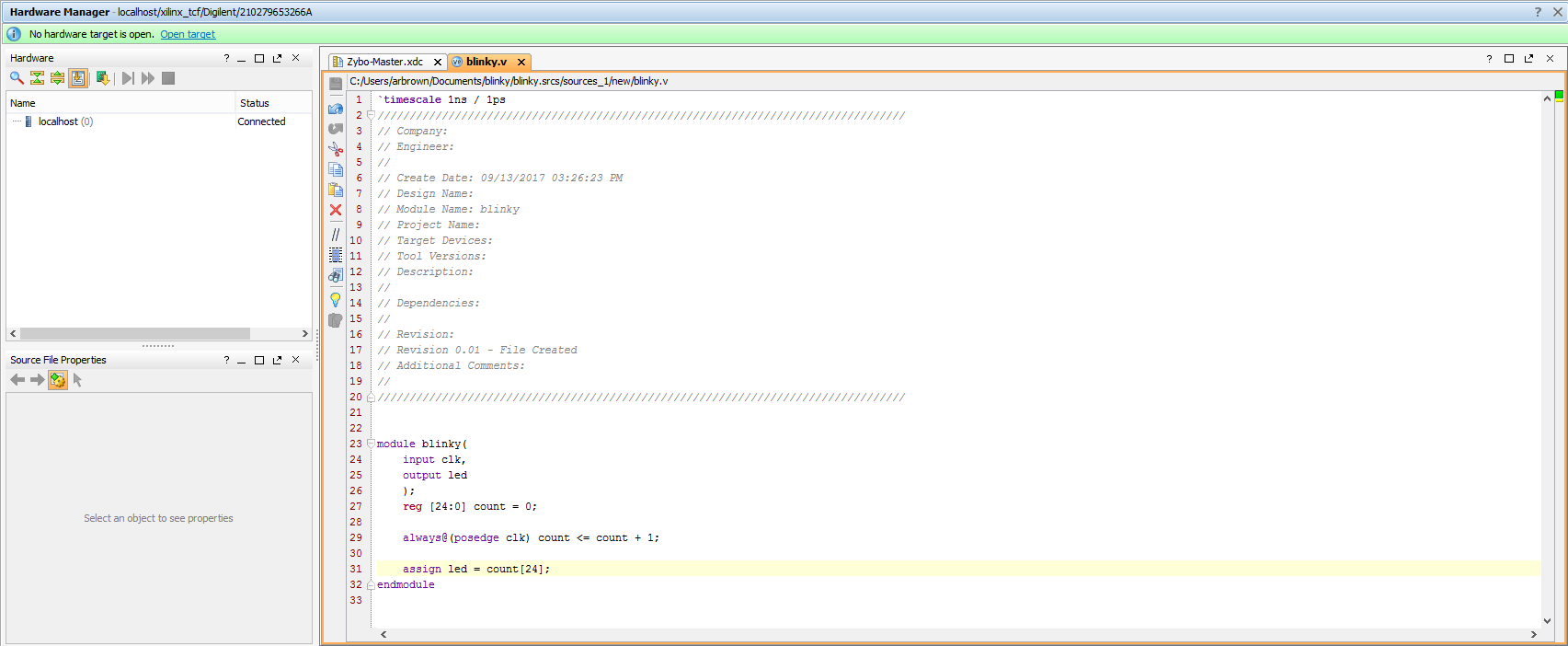

Vivado's Hardware Manager can be opened by clicking on Open Hardware Manager at the bottom of the Flow Navigator pane on the left side of the Vivado window.

The first step to programming a device is to connect the Vivado Hardware Server to it as a target. To get to the Open Hardware Target wizard click the

link in the green banner near the top of the window. From the drop-down that opens, select

link in the green banner near the top of the window. From the drop-down that opens, select  .

.

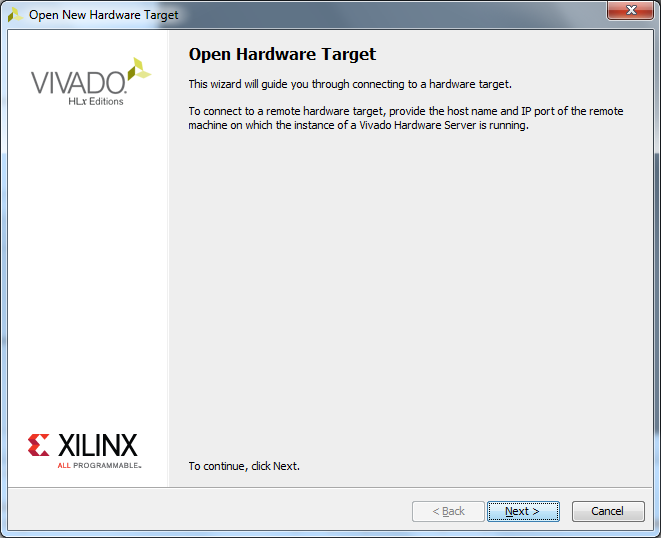

Once the wizard opens, click Next.

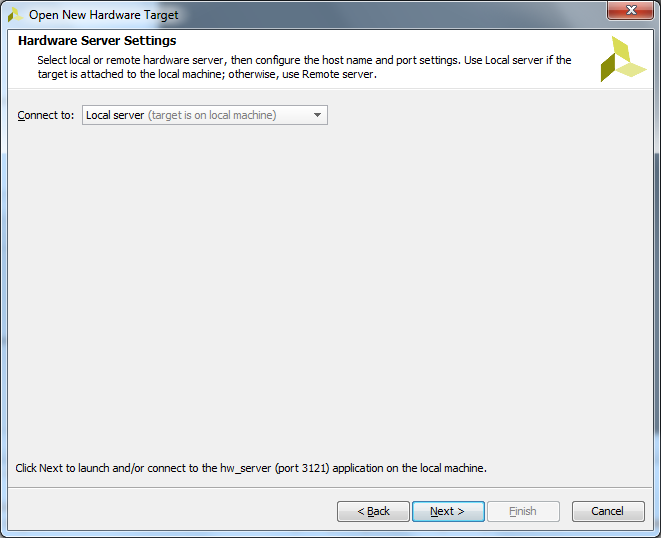

The next screen asks if the hardware server is local or remote. If the board is connected to the host computer choose local, if it is connected to another machine choose remote and fill in the Host Name and Port fields.

Click Next to continue.

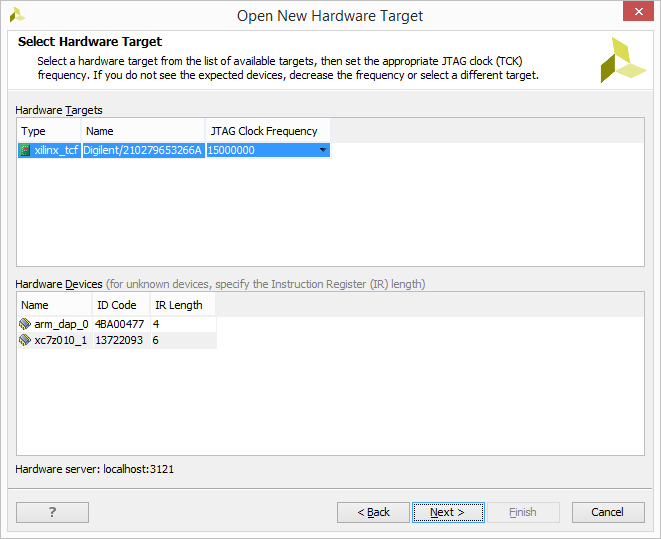

This screen gives a list of devices connected to the hardware server. If there is only one connected it will be the only device shown.

Click Next to continue.

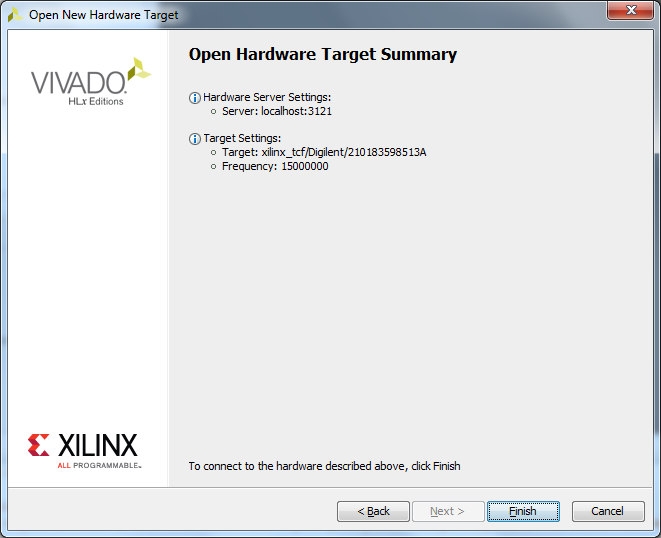

The final screen shows a summary of the options selected in the wizard. Verify the information and click Finish. The board is now connected to the hardware server.

To program the device with the bit file generated earlier, either click the

link in the green banner at the top of the window or click the

link in the green banner at the top of the window or click the  button in the Flow Navigator under

button in the Flow Navigator under  . From the drop-down that opens, select the device to program (Example:

. From the drop-down that opens, select the device to program (Example:  ) and the following window will open:

) and the following window will open:

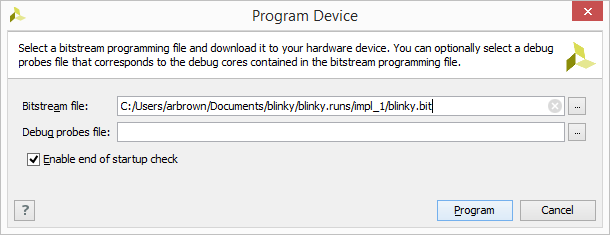

The Bitstream File field should be automatically filled in with the bit file generated earlier. If not, click the

button at the right end of the field and navigate to

button at the right end of the field and navigate to

<Project Directory>/<Project Name>.runs/impl_1/ and select the bit file (Example: ). Now click Program. This will connect to the board, clear the current configuration, and program it using the new bit file.

). Now click Program. This will connect to the board, clear the current configuration, and program it using the new bit file.

Baremetal Release (Before Programming, XSCT Scripts)

Note: This workflow is common across many Digilent FPGA demos. Screenshots may not match the demo you are working with.

Important: These steps are only to be used with releases for Xilinx tools versions 2020.1 and newer. Older releases may require other flows, as noted in the table of releases.

First, download the '*-hw.xpr.zip' and “Software source archive” files from the demo release, linked above. Note that the hardware is included in the Assets list, while the software is linked from the description of the release.

The hardware (-hw) archive contains the Vivado project used to build the hardware platform for this demo. The project can be opened, modified, and used to update the hardware platform later if so desired, but this is optional. The software archive contains the software sources, hardware description file (XSA), and a set of scripts that can be used to rebuild the workspace.

Both files should be extracted.

Note: You may notice “-sw” archives in the release's downloads list. These importable archives should be ignored - a bug in Vitis 2020.1 prevents their use in some situations, and as such, the scripted method here is to be used instead.

- Recreate a Vitis Workspace from Source

-

Important: When selecting a workspace to open Vitis into, the use of the extracted software archive's “ws” folder is recommended. The use of this folder simplifies the process of invoking the script that recreates the projects.

Select the dropdown corresponding to your operating system, below.

- Windows

- Linux

-

Open a terminal and run the following commands. The install path is /opt/Xilinx by default.

source <install_path>/Vitis/2020.1/settings64.sh vitis

Note: Regardless of OS, if Vivado is open, Vitis can also be launched through the Tools → Launch Vitis toolbar option.

Upon launching Vitis, a dialog will appear where a workspace must be chosen. The workspace is the directory where all of the projects and files for the application being developed will live. If a folder that does not currently exist is chosen, it will be created. Choose a workspace and click Launch to finish launching Vitis.

With Vitis open, in the menu bar at the top of the window, use the Xilinx → XSCT Console option to launch the Xilinx Software Command-line Tool.

In the XSCT Console, if you used the software archive's ws folder, enter the command below to run a script that recreates each of the projects and platforms associated with the demo from their sources.

source [getws]/../src/checkout.tcl

If you did not use the ws folder, find the path to the extracted archive, and enter the commands below. Note that all slashes in the path must be forward slashes (“/”) or the entire path must be enclosed in curly braces (“{}”).

source (path to software)/src/checkout.tcl

The checkout process may some time, though not more than a few minutes, as the projects are recreated and built. When complete, the “xsct%” prompt will reappear.

Baremetal Release (Before Programming)

Note: This workflow is common across many Digilent FPGA demos. Screenshots may not match the demo you are working with.

Important: These steps are only to be used with releases for Xilinx tools versions 2020.1 and newer. Older releases may require other flows, as noted in the table of releases.

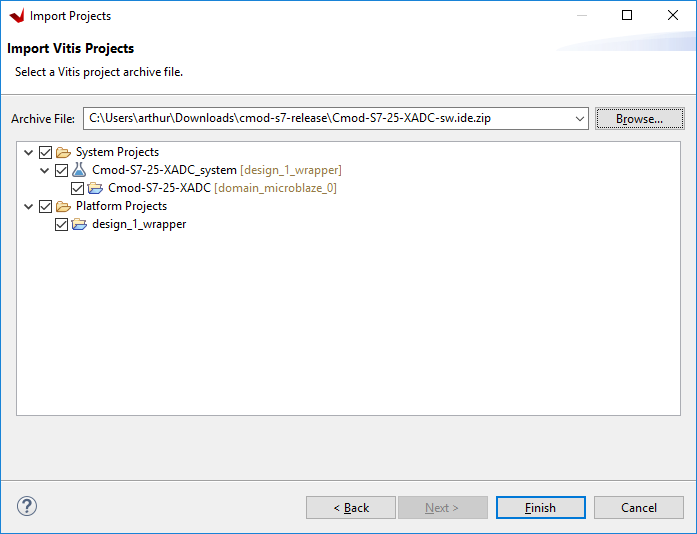

First, download the '*.xpr.zip' and '*.ide.zip' files from the demo release, linked above. The XPR archive contains the Vivado project used to build the hardware platform for this demo. The project can be opened, modified, and used to update the hardware platform later if so desired, but this is optional. The IDE archive contains a set of projects to be imported into a Vitis workspace.

Note: Unlike with Vivado XPR archives, do NOT extract the Vitis project archive ('*.ide.xip'). Vitis imports sources from the archive file directly.

- Import Vitis Projects from a Release

-

Select the dropdown corresponding to your operating system, below.

- Windows

- Linux

-

Open a terminal and run the following commands. The install path is /opt/Xilinx by default.

source <install_path>/Vitis/2020.1/settings64.sh vitis

Note: Regardless of OS, if Vivado is open, Vitis can also be launched through the Tools → Launch Vitis toolbar option.

Upon launching Vitis, a dialog will appear where a workspace must be chosen. The workspace is the directory where all of the projects and files for the application being developed will live. If a folder that does not currently exist is chosen, it will be created. Choose a workspace and click Launch to finish launching Vitis.

- Build a Vitis Application

-

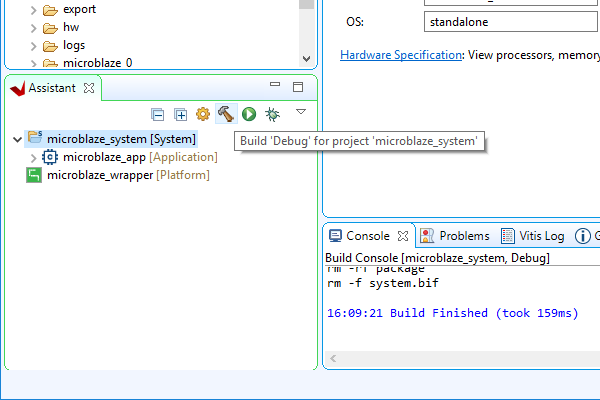

Once an application project has been set up and includes all necessary sources, it should be built. To build the project and all of its dependencies, select the [System] project in the Assistant pane, and either click the Build button (

), or press Ctrl-B on your keyboard.

), or press Ctrl-B on your keyboard.

Note: There are three types of build targets in the Assistant pane, Platforms, Systems, and Applications. Building the application will not trigger any other applications in the system to be built, but will build the wrapper as a dependency. Building the platform will only build the platform, as it has no dependencies. Building the system causes each application in the system, as well as the platform, to be built.

This process may take several minutes to complete. When done, the Console tab at the bottom of the window will display a “Build Finished” message.

Baremetal Release (No Build)

Note: This workflow is common across many Digilent FPGA demos. Screenshots may not match the demo you are working with.

Important: These steps are only to be used with releases for Xilinx tools versions 2020.1 and newer. Older releases may require other flows, as noted in the table of releases.

First, download the '*.xpr.zip' and '*.ide.zip' files from the demo release, linked above. The XPR archive contains the Vivado project used to build the hardware platform for this demo. The project can be opened, modified, and used to update the hardware platform later if so desired, but this is optional. The IDE archive contains a set of projects to be imported into a Vitis workspace.

Note: Unlike with Vivado XPR archives, do NOT extract the Vitis project archive ('*.ide.xip'). Vitis imports sources from the archive file directly.

- Import Vitis Projects from a Release

-

Select the dropdown corresponding to your operating system, below.

- Windows

- Linux

-

Open a terminal and run the following commands. The install path is /opt/Xilinx by default.

source <install_path>/Vitis/2020.1/settings64.sh vitis

Note: Regardless of OS, if Vivado is open, Vitis can also be launched through the Tools → Launch Vitis toolbar option.

Upon launching Vitis, a dialog will appear where a workspace must be chosen. The workspace is the directory where all of the projects and files for the application being developed will live. If a folder that does not currently exist is chosen, it will be created. Choose a workspace and click Launch to finish launching Vitis.

Baremetal Release (No Build, Direct File Download)

Note: This workflow is common across many Digilent FPGA demos. Screenshots may not match the demo you are working with.

Important: These steps are only to be used with releases for Xilinx tools versions 2020.1 and newer. Older releases may require other flows, as noted in the table of releases.

First, download the '*.xpr.zip' and '*.ide.zip' files, linked above. The XPR archive contains the Vivado project used to build the hardware platform for this demo. The project can be opened, modified, and used to update the hardware platform later if so desired, but this is optional. The IDE archive contains a set of projects to be imported into a Vitis workspace.

Note: Unlike with Vivado XPR archives, do NOT extract the Vitis project archive ('*.ide.xip'). Vitis imports sources from the archive file directly.

- Import Vitis Projects from a Release

-

Select the dropdown corresponding to your operating system, below.

- Windows

- Linux

-

Open a terminal and run the following commands. The install path is /opt/Xilinx by default.

source <install_path>/Vitis/2020.1/settings64.sh vitis

Note: Regardless of OS, if Vivado is open, Vitis can also be launched through the Tools → Launch Vitis toolbar option.

Upon launching Vitis, a dialog will appear where a workspace must be chosen. The workspace is the directory where all of the projects and files for the application being developed will live. If a folder that does not currently exist is chosen, it will be created. Choose a workspace and click Launch to finish launching Vitis.

Baremetal Release (Programming)

- Launch a Vitis Application

-

Make sure your board is set to boot from JTAG before it's powered on. JTAG programming can override other boot modes on some devices, but it's easier to tell when a project is programmed into the board if there isn't already one in there.

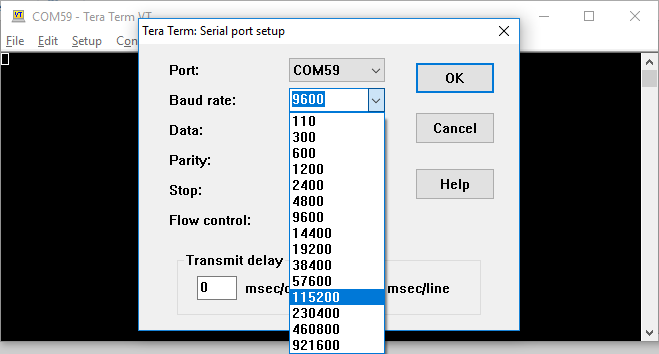

First, many applications require that a serial console is connected to the board, so that standard output (from print statements) can be viewed. For this purpose, a serial terminal should be used. Use a serial terminal application to connect to the board's serial port. Unless otherwise stated, Zynq designs use a baud rate of 115200 and Microblaze designs with an AXI UART Lite IP use a baud rate of 9600. Flow control should be set to NONE.

Note: While Vitis has a built in serial terminal included in its Debug view, it sends characters to a board on a line-by-line basis. Some software examples require the use of character-by-character reception of data. Tera Term or PuTTY are recommended if you are not sure what will work.

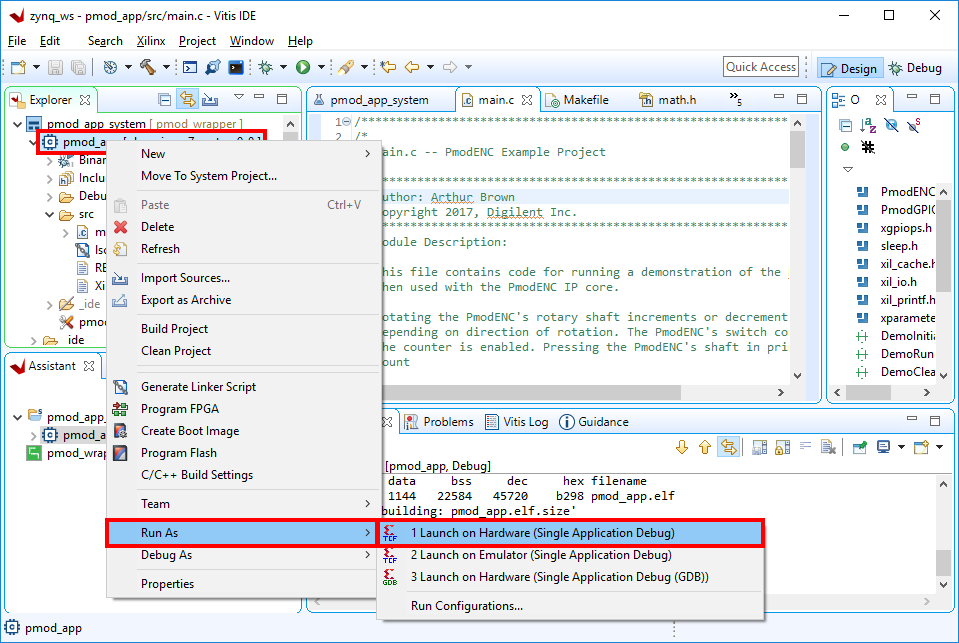

In the Explorer pane at the left side of the screen, right click on the application or system project that is to be run, and select Run as → 1 Launch on Hardware (Single Application Debug). The FPGA will be programmed with the bitstream, the ELF file created by the software build is loaded into system memory, and the application project will begin to run. You will need to click back over to the Vitis Serial Terminal from the Console tab.

Note: Once the project has been run at least once, you can use the green run button (

) in the toolbar at the top of the screen to program the board instead.

) in the toolbar at the top of the screen to program the board instead.

Baremetal Update Specification

In order to modify and switch out the hardware platform for a baremetal demo, you should first open the Vivado project from the release. Extract the previously downloaded '*.xpr.zip' file.

- Open a Block Design Project in Vivado

-

Launch Vivado

Select the dropdown corresponding to your operating system, below.

- Windows

- Linux

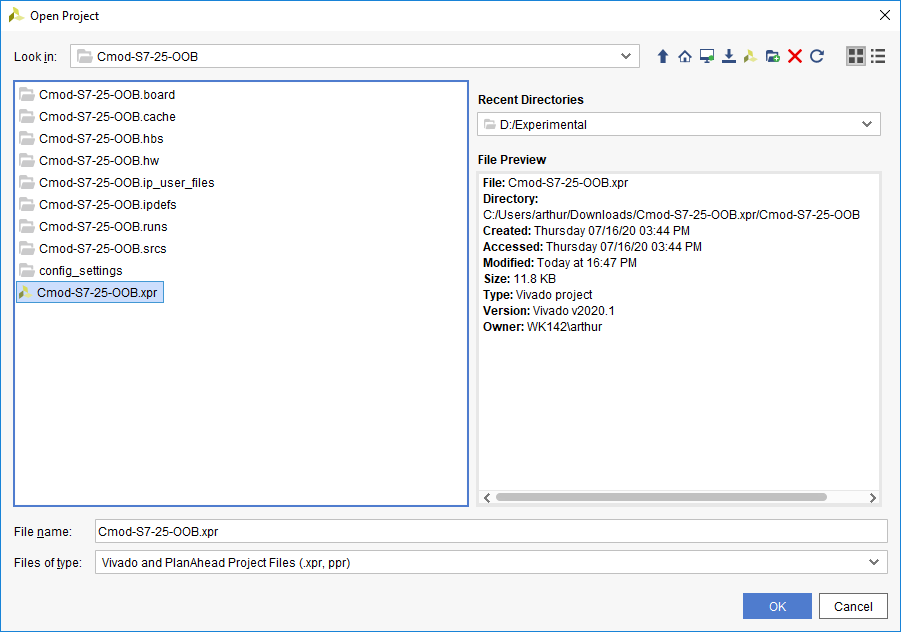

In Vivado's welcome screen, use the Open Project button to navigate to and open the XPR file contained in the folder the release was extracted into.

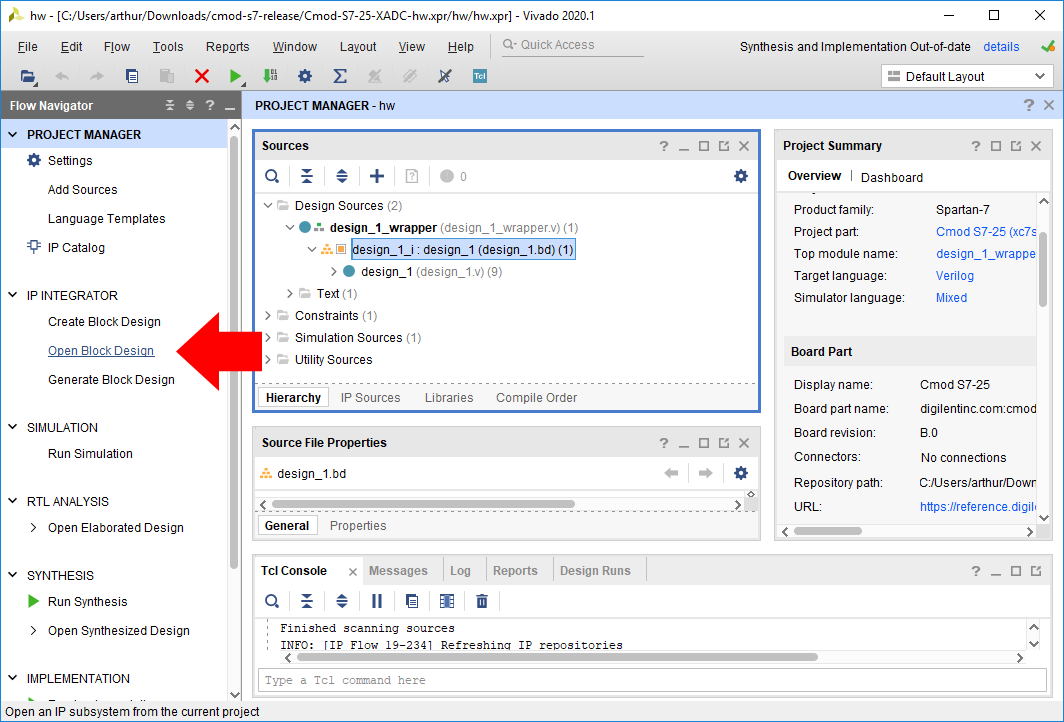

The project's block diagram, which contains the design, with all of the existing components and their connections, can be opened by either double-clicking on the “*.bd” file in the sources pane (which also includes other source files, such as constraints), or by clicking the Open Block Design button in the Flow Navigator pane.

Making changes to the design is out of the scope of this particular document. More information on how to use IP Integrator to create or modify a project can be found through Getting Started with Vivado and Vitis for Baremetal Software Projects. The remainder of this document will discuss how to generate a bitstream, export a new hardware platform, and load it into Vitis.

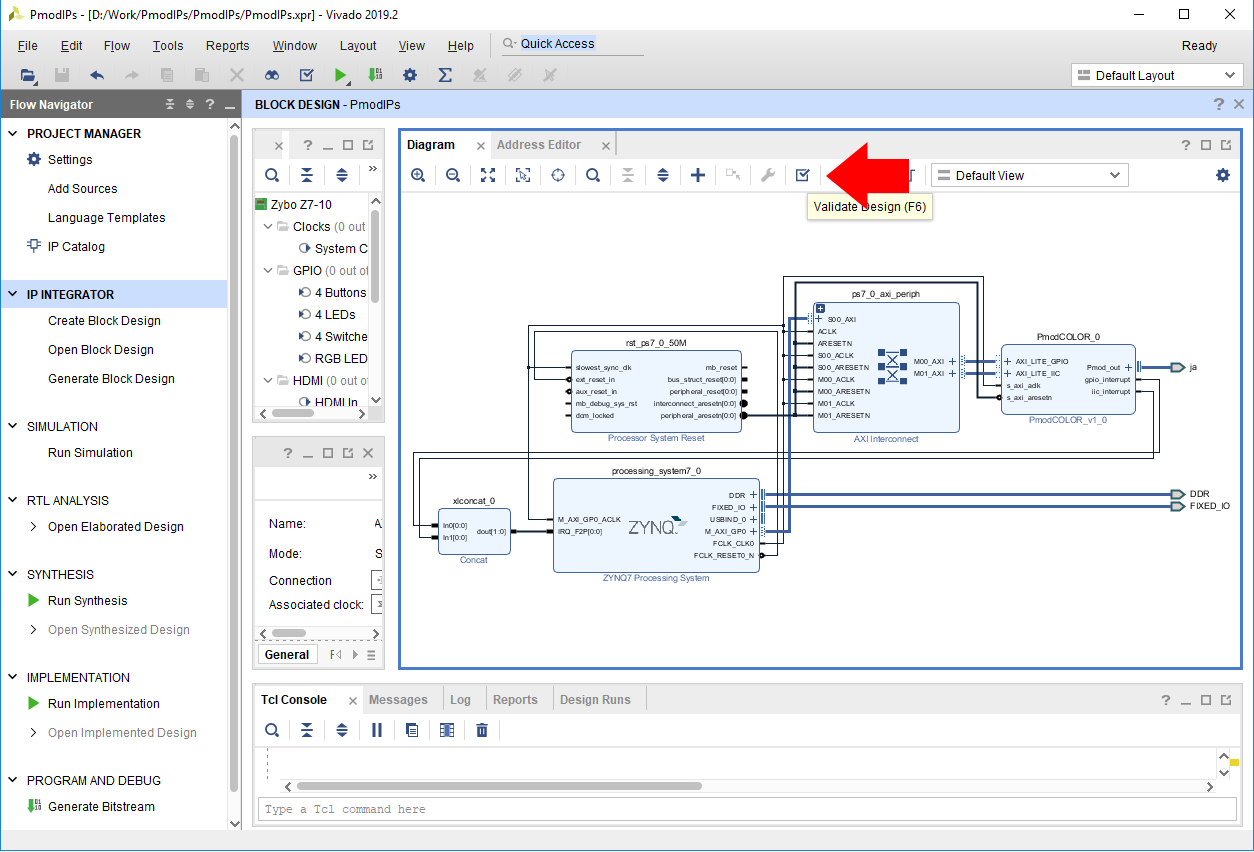

Before the Vivado project can be built, the block design must be validated. This step runs an automatic check of the block design to see if there are any potential issues with it. Click the Validate Design button (

) in the Diagram pane's toolbar (or press the F6 key).

) in the Diagram pane's toolbar (or press the F6 key).

If the design has issues, a dialog will pop up that lists them. It should be noted that most Warnings can be ignored, as can some Critical Warnings. These issues can also be viewed in the Messages tab of the pane at the bottom of the window.

If there are no issues, a dialog will pop up that will tell you so. Click OK to continue.

Note: Some Zynq boards may produce critical warnings at this stage relating to PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY parameters. These warnings are ignorable and will not affect the functionality of the project. See the Hardware Errata section of your board's reference manual for more information.

- Build a Vivado Project

-

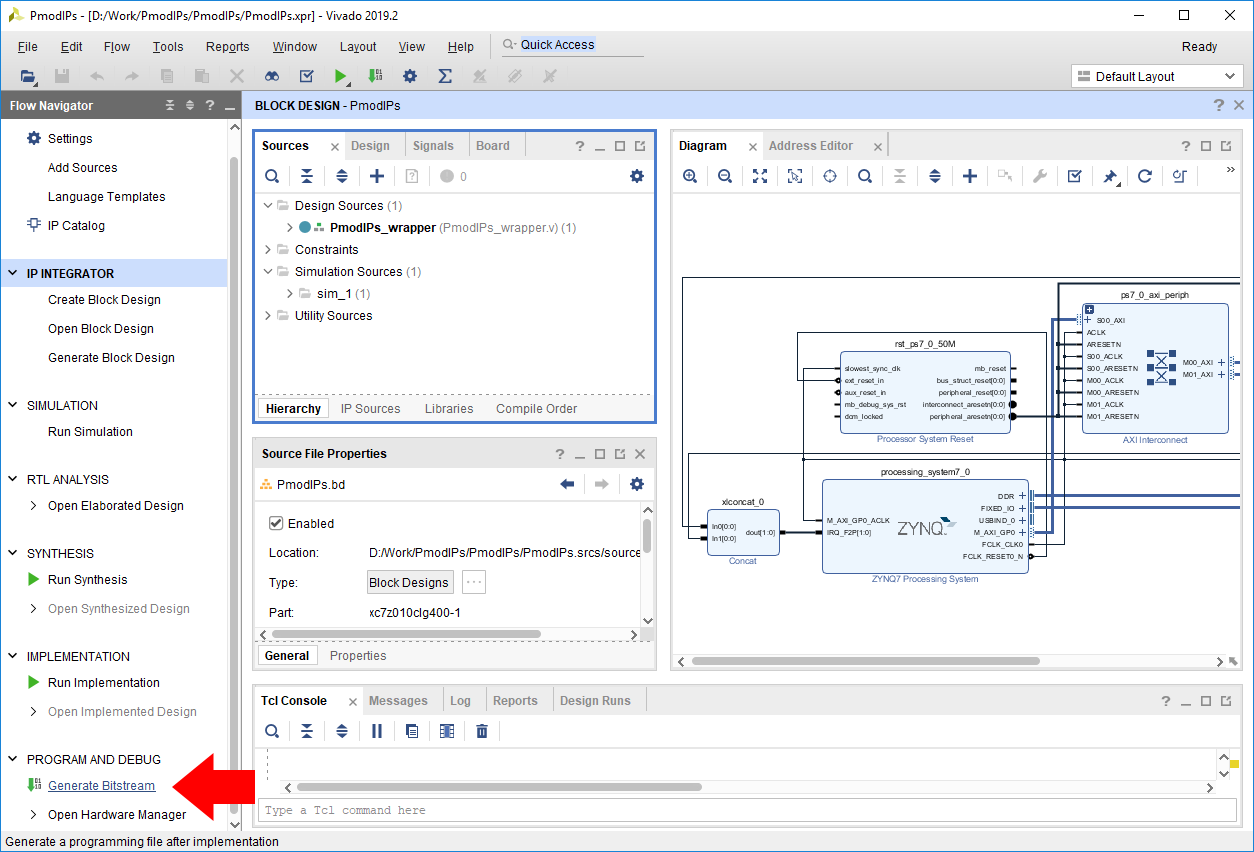

At this point, the Vivado Project is ready to be built, by running it through Synthesis and Implementation, and finally generating a bitstream. Click the Generate Bitstream button in the Program and Debug section of the Flow Navigator pane at the left side of the window.

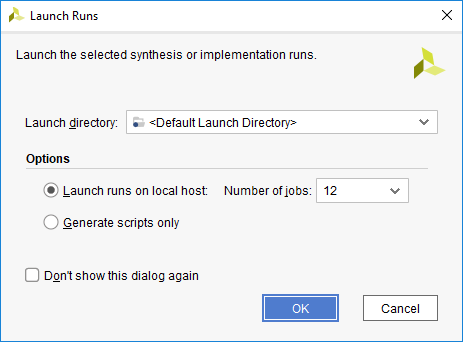

A dialog will pop up with several options for how Synthesis and Implementation should be run. Most should be left as defaults. Of particular importance is the Number of jobs dropdown, which is used to specify how much of the resources of your computer should be dedicated to the build. A larger number of jobs will dedicate more resources, which will allow the build to be completed faster. It is recommended to choose the highest available number.

Note: Critical warnings about how IPs included within another IP were packaged with a different board value can be safely ignored. The same is true for warnings related to negative CK-to-DQS delays seen on some Zynq boards.

Depending on the complexity of the design, the board used, and the strength of your computer, the process of building the project can take between 5 and 60 minutes.

When complete, a dialog will pop up that presents several options for what to do next:

- Open Implemented Design can be used to view the actual hardware design that has been implemented and will be placed onto the chip.

- View Reports can be used to view additional information about the design, including how much of the resources of the FPGA will be used by the design.

- Open Hardware Manager can be used to go directly to Vivado's Hardware Manager, which can be used to program a hardware design onto a board. This is typically used for designs that do not involve a software component.

- Generate Memory Configuration File can be used to create a file for programming an FPGA-only design into flash memory.

If none of these options are desired, click Cancel to continue.

- Export a Hardware Platform

-

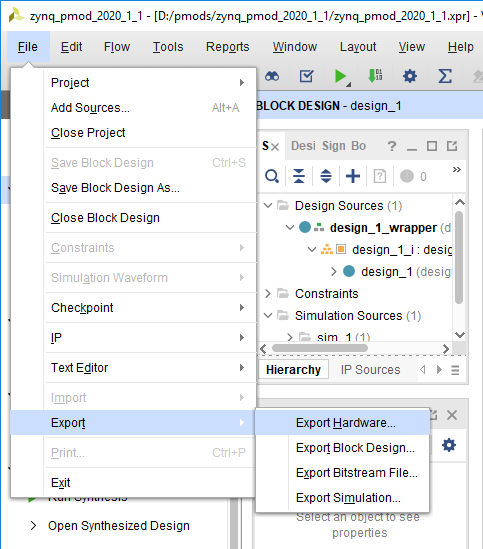

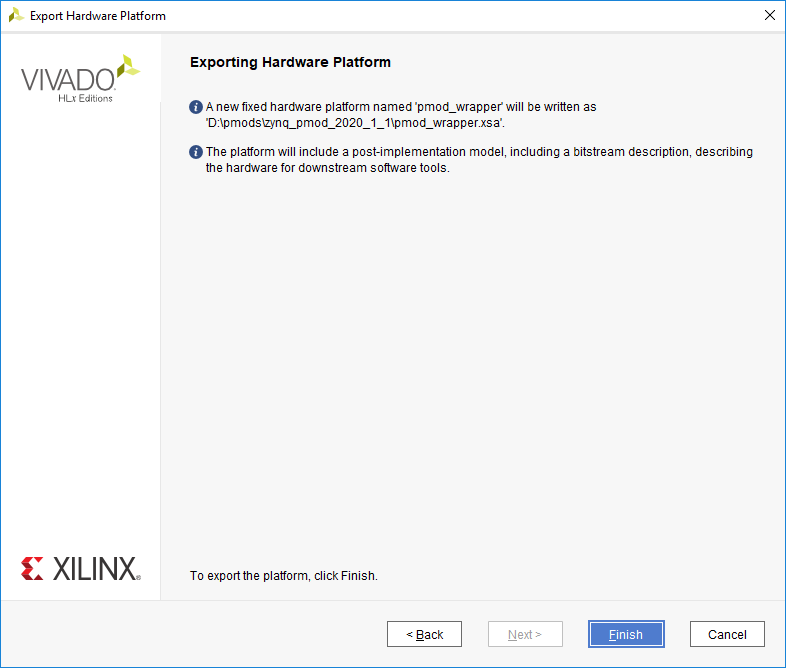

Once the project has been built, the design must be exported from Vivado so that Vitis has access to information about the hardware that a software application is being developed for. This includes the set of IP connected to the processor, their drivers, their addresses, and more. Exporting hardware after the bitstream has been generated allows you to program your board directly from within Vitis.

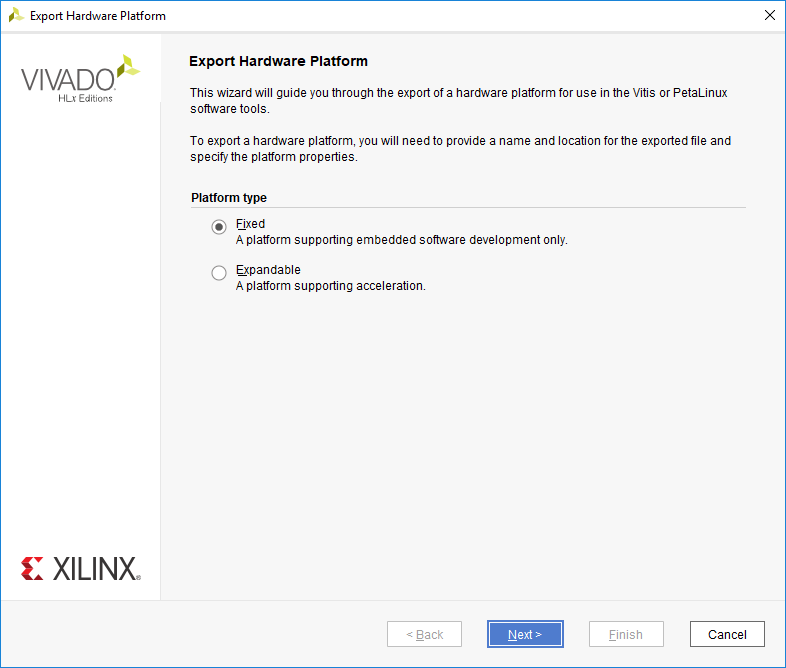

The wizard that pops up guides you through the options available for hardware export. The first screen allows you to select a Fixed or Expandable platform. In this case, choose a Fixed platform and click Next to continue.

This screen is not present in Vivado 2022.1, proceed to the next

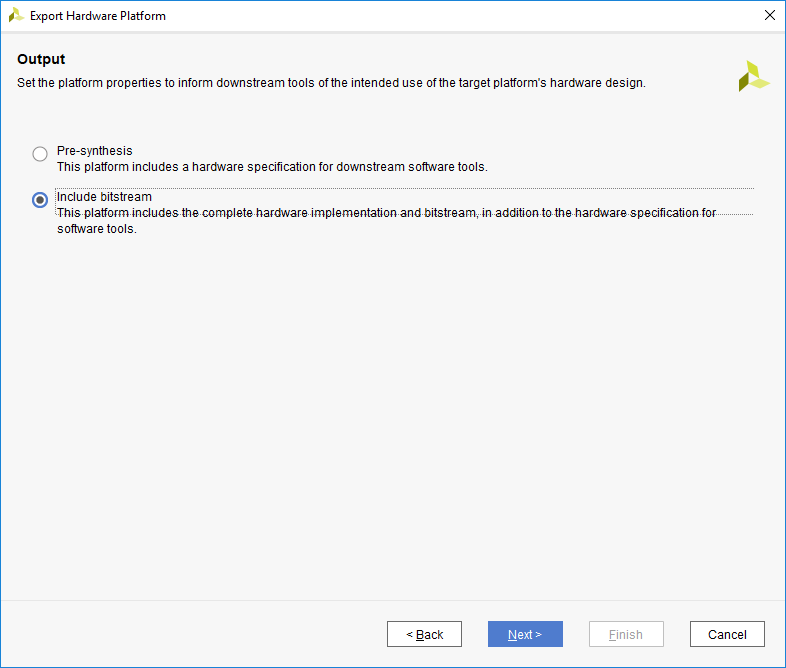

The Output screen allows you to select whether only the hardware specification (Pre-synthesis) should be exported, or whether the bitstream should be included. Since the bitstream has already been generated, it should be included in the platform so that Vitis can automatically figure out where it is when programming a board. Select Include bitstream and click Next to continue.

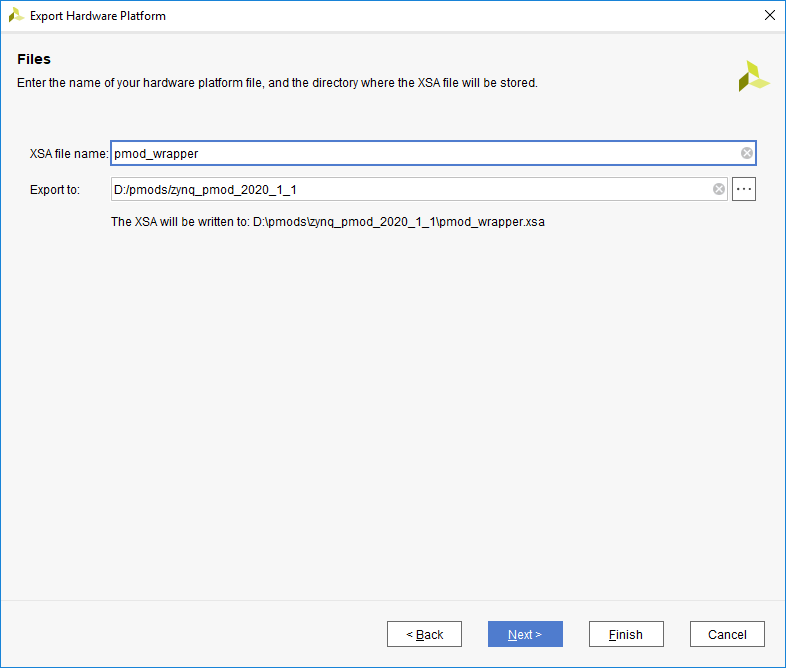

The Files screen gives you the option to choose a name for the Xilinx Shell Architecture (XSA) file, and provide a path to a folder that the file will be placed within. Give your XSA file a name, and choose a memorable location to place it in. This file will later be imported into Vitis, so take a note of where it is placed and what it is called.

Important: Do not use spaces in the file name or export path. Underscores or camelCase are recommended instead.

Click Next to continue.

- Update a Hardware Platform in Vitis

-

If a hardware design is changed after having created a Vitis application project, several steps must be taken in order to update the Vitis workspace with a newly exported XSA file. The XSA file contains all of the information relevant to Vitis about the hardware platform, and changing a platform project's specification based on this file will automatically load in any changes. This includes adding new drivers for new IP that have been installed and changing the files that define the addresses and other details of any installed IP that may have been renamed or had their addresses changed.

These steps assume that you have already regenerated the bitstream and reexported hardware in the same way that would be done prior to creating a new Vitis workspace.

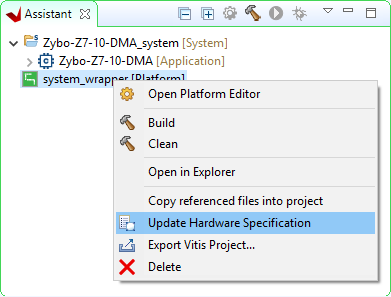

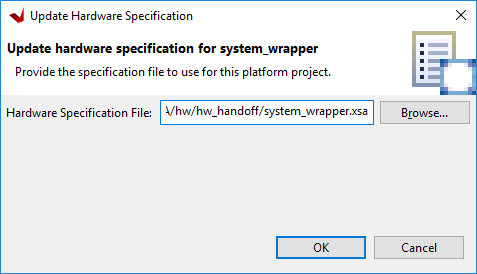

Within Vitis' Assistant pane, find the platform project that you wish to update with the new hardware. This project will typically have a name that ends with “_wrapper”, and is marked with the text “[Platform]”.

Right click on this project and select Update Hardware Specification.

In the dialog that pops up, click Browse, and navigate to the location of the XSA file that you want the platform to target. Click Open to select this file.

Double check that the Hardware Specification File path matches that of the XSA file you want to use, then click OK to start the automatic process of updating the platform.

When complete, a dialog will pop up to state that the platform project has been updated. Click OK to acknowledge this.

At this point, changes to the hardware specification have been loaded into the hardware platform. The bitstream will have been updated, if it was loaded into the XSA file. The set of drivers and the xparameters file will have changed to match what is in the modified design. Changes to the software application may be required before the application can be built and programmed onto the board, however, detailing what may need to be done is outside of the scope of this guide.

Petalinux Release (Before Programming)

Note: This workflow is common across many Digilent Petalinux demos. Screenshots may not match the demo you are working with.

Important: These steps are only to be used with releases for Xilinx tools versions 2020.1 and newer. Older releases may require other flows, as noted in the table of releases.

First, download the '*.bsp' file from the demo release, linked above.

- Open a Petalinux Project from a Release

-

Open a terminal and run the following commands. The install path is /opt/pkg/petalinux/ as exemplified in UG1144 v.2020.1. This will set up the Petalinux environment for this terminal only.

source <path-to-installed-PetaLinux>/settings.sh

In the same terminal navigate to the desired project folder and create the Petalinux project using the '*.bsp' by executing the following command. The resulting folder structure will contain a pre-built folder which has the necessary boot binaries for the current Demo

cd <path-to-project-folder> petalinux-create -t project -s <path-to-bsp>

- Build a Petalinux Project

-

In order to rebuild the project without changing anything in the configuration, first navigate to the root of the Petalinux project using the terminal which has the Petalinux environment set up.

Note: If the Petalinux environment is not set up it will not recognize the petalinux-* commands.

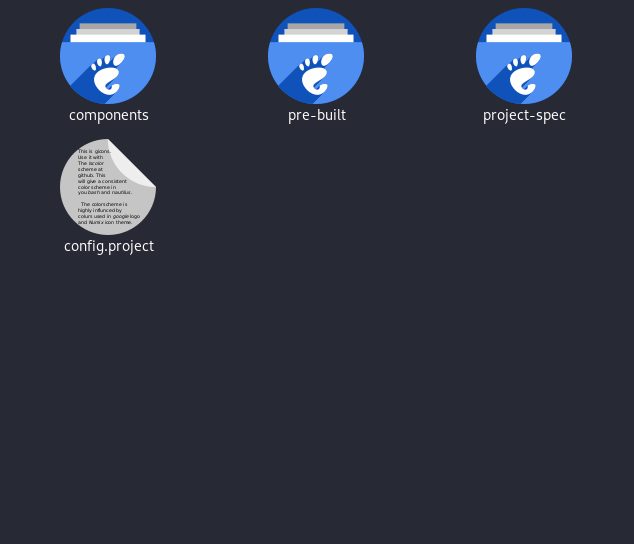

The root folder will contain the following folders and file: components, project-spec, pre-built (optional), config.project. Once in this folder execute the build command. This will start building the Petalinux project based on the current configuration. The execution time of the build command will depend on PC performance, project complexity, execution iteration (it takes longer for a clean project to build). Depending on the project complexity after the build, the project folder might take several GB of free space.

petalinux-build

After the build completion, the Boot.bin has to be explicitly built in order to have a Second Stage Boot Loader (SSBL) from Petalinux. This can be obtained by executing the command below from the root folder.

Note: <zynq_type> may vary depending on Zynq7000 or Zynq Ultra Scale

petalinux-package --boot --force --fsbl images/linux/<zynq_type>_fsbl.elf --fpga images/linux/system.bit --u-boot

Petalinux Release (Programming)

- Booting Petalinux on a Zynq Board

-

Copy the BOOT.BIN, boot.scr, image.ub files from the <path-to-project-folder>/images/linux or the <path-to-project-folder>/pre-built folder onto a FAT32 formatted MicroSD Card. Once this has been done, safely remove the SD Card from the PC and slide it into the development board's MicroSD Card slot. Make sure that the board is set up to boot from SD Card.

Note: Some projects might contain an extra file, uEnv.txt, which should be added to the SD Card

Boot up the board and set up your preferred serial console to listen on the serial port using the default baud rate of 115200. On the console, you should be able to see the boot-up sequence of the board starting from U-Boot (SSBL) up to the login prompt of Linux.

Note: The default login username and password is root:root

Petalinux Configurations

Note: This a brief summary of what Petalinux can do. For more details please refer to the UG1144 v.2020.1

There are some components that can be modified in Petalinux in order to customize your Linux environment. These include the user space application, kernel drivers, u-boot configuration, generic Petalinux settings, and Hardware update components. Most of these changes can be done by executing the petalinux-config command with different parameters.

Note: By using petalinux-config -c <COMPONENT> the component changes will be stored in the workspace directory (<project-root-dir>/components/yocto/workspace). To apply workspace changes to the recipe in the meta-user, the user must run the -x finish command to return their build location, for example, “petalinux-build -c <COMPONENT> -x finish”.

- Making Hardware Changes and Adding Them to Petalinux

-

In order to modify and switch out the hardware platform for a baremetal demo, you should first open the Vivado project from the release. Extract the previously downloaded '*.xpr.zip' file. Exporting the Vivado project for Petalinux is the same as exporting it for Vitis, therefore the instructions are identical.

- Open a Block Design Project in Vivado

-

Launch Vivado

Select the dropdown corresponding to your operating system, below.

- Windows

- Linux

In Vivado's welcome screen, use the Open Project button to navigate to and open the XPR file contained in the folder the release was extracted into.

The project's block diagram, which contains the design, with all of the existing components and their connections, can be opened by either double-clicking on the “*.bd” file in the sources pane (which also includes other source files, such as constraints), or by clicking the Open Block Design button in the Flow Navigator pane.

Making changes to the design is out of the scope of this particular document. More information on how to use IP Integrator to create or modify a project can be found through Getting Started with Vivado and Vitis for Baremetal Software Projects. The remainder of this document will discuss how to generate a bitstream, export a new hardware platform, and load it into Vitis.

Before the Vivado project can be built, the block design must be validated. This step runs an automatic check of the block design to see if there are any potential issues with it. Click the Validate Design button (

) in the Diagram pane's toolbar (or press the F6 key).

) in the Diagram pane's toolbar (or press the F6 key).

If the design has issues, a dialog will pop up that lists them. It should be noted that most Warnings can be ignored, as can some Critical Warnings. These issues can also be viewed in the Messages tab of the pane at the bottom of the window.

If there are no issues, a dialog will pop up that will tell you so. Click OK to continue.

Note: Some Zynq boards may produce critical warnings at this stage relating to PCW_UIPARAM_DDR_DQS_TO_CLK_DELAY parameters. These warnings are ignorable and will not affect the functionality of the project. See the Hardware Errata section of your board's reference manual for more information.

- Build a Vivado Project

-

At this point, the Vivado Project is ready to be built, by running it through Synthesis and Implementation, and finally generating a bitstream. Click the Generate Bitstream button in the Program and Debug section of the Flow Navigator pane at the left side of the window.

A dialog will pop up with several options for how Synthesis and Implementation should be run. Most should be left as defaults. Of particular importance is the Number of jobs dropdown, which is used to specify how much of the resources of your computer should be dedicated to the build. A larger number of jobs will dedicate more resources, which will allow the build to be completed faster. It is recommended to choose the highest available number.

Note: Critical warnings about how IPs included within another IP were packaged with a different board value can be safely ignored. The same is true for warnings related to negative CK-to-DQS delays seen on some Zynq boards.

Depending on the complexity of the design, the board used, and the strength of your computer, the process of building the project can take between 5 and 60 minutes.

When complete, a dialog will pop up that presents several options for what to do next:

- Open Implemented Design can be used to view the actual hardware design that has been implemented and will be placed onto the chip.

- View Reports can be used to view additional information about the design, including how much of the resources of the FPGA will be used by the design.

- Open Hardware Manager can be used to go directly to Vivado's Hardware Manager, which can be used to program a hardware design onto a board. This is typically used for designs that do not involve a software component.

- Generate Memory Configuration File can be used to create a file for programming an FPGA-only design into flash memory.

If none of these options are desired, click Cancel to continue.

- Export a Hardware Platform

-

Once the project has been built, the design must be exported from Vivado so that Vitis has access to information about the hardware that a software application is being developed for. This includes the set of IP connected to the processor, their drivers, their addresses, and more. Exporting hardware after the bitstream has been generated allows you to program your board directly from within Vitis.

The wizard that pops up guides you through the options available for hardware export. The first screen allows you to select a Fixed or Expandable platform. In this case, choose a Fixed platform and click Next to continue.

This screen is not present in Vivado 2022.1, proceed to the next

The Output screen allows you to select whether only the hardware specification (Pre-synthesis) should be exported, or whether the bitstream should be included. Since the bitstream has already been generated, it should be included in the platform so that Vitis can automatically figure out where it is when programming a board. Select Include bitstream and click Next to continue.

The Files screen gives you the option to choose a name for the Xilinx Shell Architecture (XSA) file, and provide a path to a folder that the file will be placed within. Give your XSA file a name, and choose a memorable location to place it in. This file will later be imported into Vitis, so take a note of where it is placed and what it is called.

Important: Do not use spaces in the file name or export path. Underscores or camelCase are recommended instead.

Click Next to continue.

- Importing the New Hardware

-

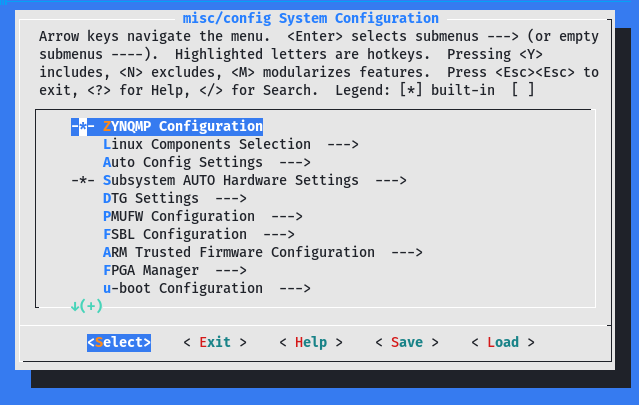

In order to import the new hardware description to Petalinux, the following command must be executed. This will prompt a configuration window where all the new Zynq generic changes for the new hardware will be visible.

petalinux-config --get-hw-description=<path-to-new-xsa>

Other changes which can be configured from this window are: boot-flow, default password, FPGA reconfiguration, image packaging, and other important settings. This window can also be accessed by simply executing petalinux-config without any parameters.

petalinux-config

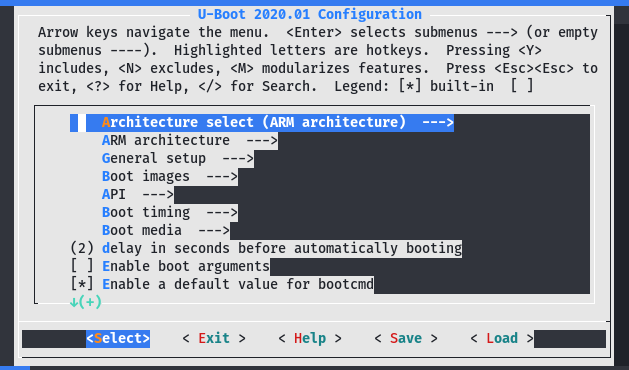

- Configuring U-boot

-

When first importing the hardware, some U-boot customization is generated by the import feature. U-boot customization includes drivers for boot mediums, file system support, boot console arguments, network support, and many more. In order to bring up the configuration window, the following command must be executed.

petalinux-config -c u-boot

- Configuring the Kernel

-

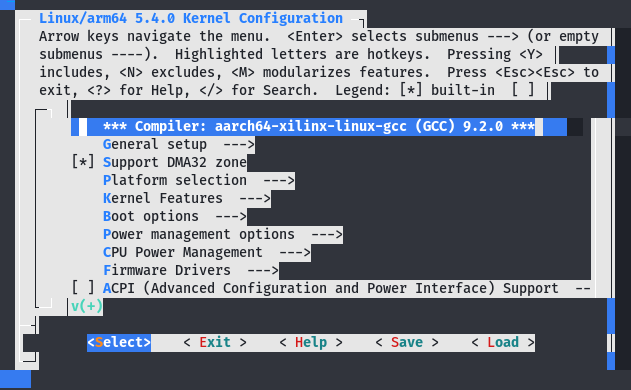

When first importing the hardware, some kernel customization is generated by the import feature, which usually includes supported drivers for PL IPs. U-boot customization includes drivers for drivers, logging levels, debugging flags, and many more. In order to bring up the configuration window, the following command must be executed:

petalinux-config -c kernel

- Configuring the RootFS

-

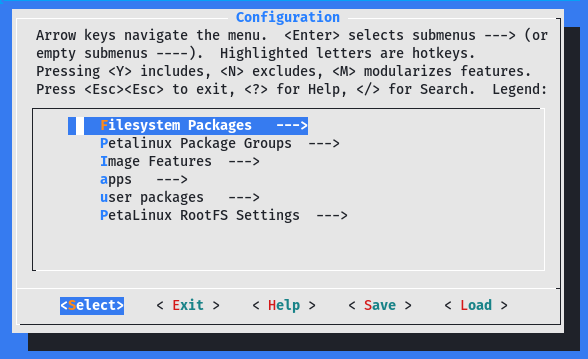

The packages which will be built into the rootfs need to be added manually by the user. The default package manager for Petalinux currently is RPM and any additional packages which the user wants to add need to be built using Petalinux. In order to bring up the configuration window, the following command must be executed:

petalinux-config -c rootfs

- Changes to the Device Tree

-

When first building the project by executing petalinux-build or if you are using the *.bsp version of the project, the generated device tree will be available in <path-to-project-folder>/components/plnx_workspace/device-tree/device-tree. Any changes to this folder will be overwritten at the next build. In order to make permanent changes, the <path-to-project-folder>/project-spec/meta-user/recipes-bsp/device-tree/files/*.dtsi need to be changed.

Note: Changes to the device tree components will have to be done by referring to the already existing nodes in the auto-generated device trees.

Warning

After configuring some of the previous settings might be lost. This is a known issue in Petalinux 2019.2 and 2020.1; more information about the workaround can be found here: Xilinx Support Case

Baremetal Release Workaround (Before programming)

- Apply Fix for Linker Script Import Bug

-

Due to a bug in some versions of Xilinx's Vitis IDE, two more steps are needed for the project to import correctly. If your projects build without errors, ignore this section.

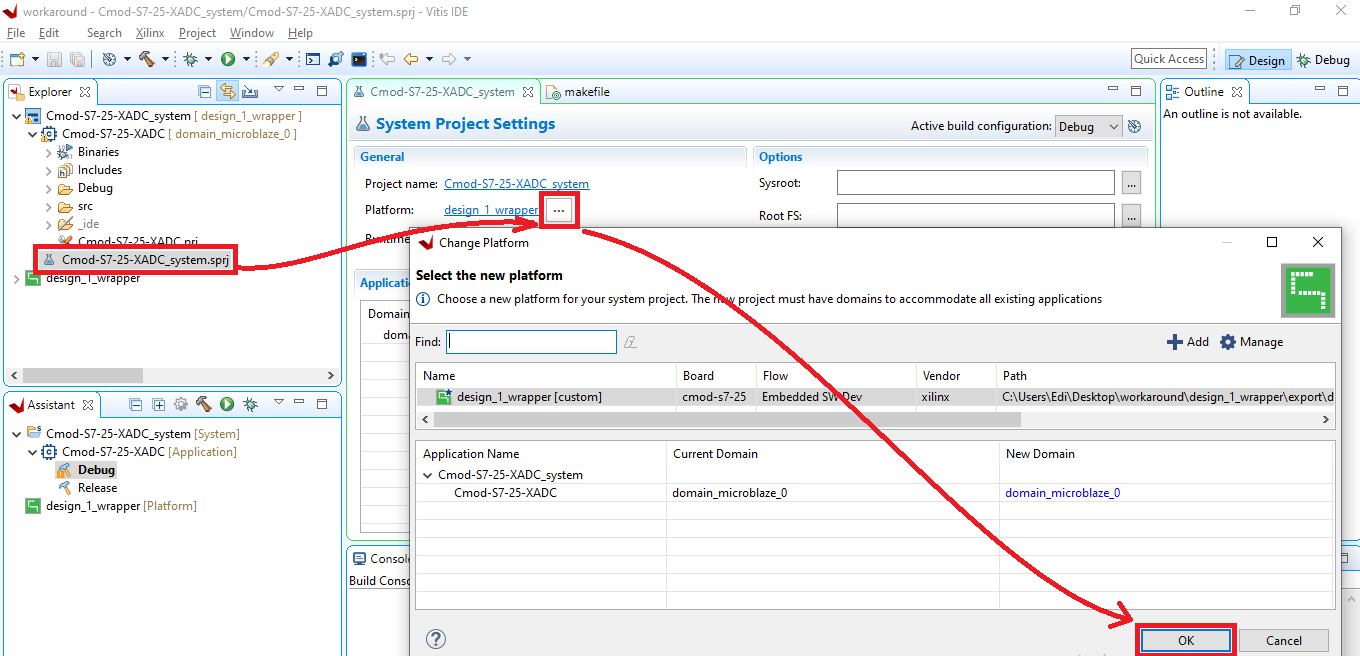

After importing the project, open the .sprj file. In the System Project Settings, select a platform by clicking on the

…icon, as shown in the image. Select the platform presented and click Ok.

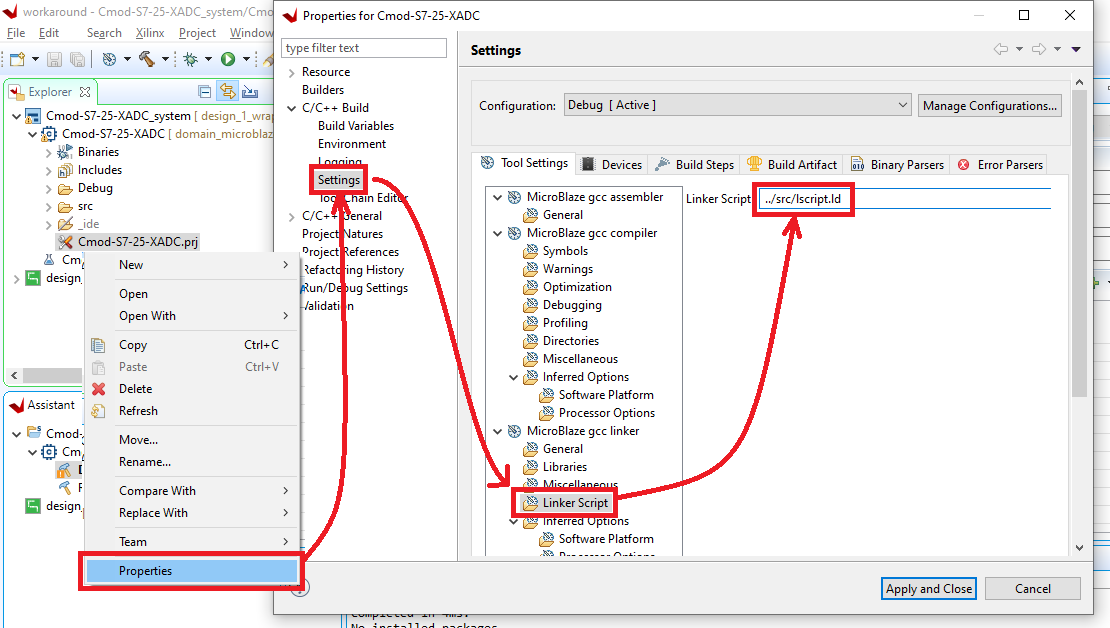

Right click on the .prj file and select Properties. In the opened window, go into C/C++ Build and select Settings, as shown in the image. After opening the Settings tab, select Linker Script and change the existing path to

../src/lscript.ld. Click Apply and Close.The project is now imported correctly.